The 2026 Engineer’s Guide: Choosing the Right MCU for Your Next IoT & New Energy Project

For battery-powered edge devices and high-frequency motor control systems, raw clock speed and baseline sleep currents are misleading metrics. An MCU featuring a 400MHz core and a 20nA deep-sleep mode provides no practical advantage if it requires 200µs to restore its clock trees before executing an interrupt. True engineering value is determined by the total cost of ownership, which encompasses unit price, development time, tooling costs, and the prototype-to-production pain associated with hardware abstraction layer (HAL) bloat. This 2026 MCU selection guide, IoT and New Energy microcontrollers breakdown analyzes the current silicon landscape across STMicroelectronics, NXP, Microchip, and emerging RISC-V architectures to help embedded systems developers avoid spinning boards with the wrong architecture.

The 2026 MCU Selection Guide, IoT and New Energy Microcontrollers: Total Cost of Ownership Framework

The total cost of ownership for a microcontroller extends beyond the unit price to include development time, tooling expenses, ecosystem maturity, long-term availability, and the engineering hours required to transition from prototype to production.

📺 Top 5 Microcontrollers in 2026 - Best Performance for the Price

The Total Cost Formula: Unit Price vs. Deployment Friction

Procurement teams often evaluate microcontrollers based on volume pricing, but firmware engineers bear the cost of deployment friction. Experts point out that "bang for your buck" is not about picking the lowest cost chip; it is about maximizing what you get for your money by factoring in the entire deployment lifecycle. A chip that saves $0.20 on the bill of materials (BOM) but requires an additional three months of firmware debugging due to poor documentation ultimately yields a negative return on investment.

The Integration Paradox

Modern silicon vendors frequently pack microcontrollers with extensive peripheral arrays to appeal to the broadest possible market. Consequently, this creates an "Integration Paradox." Over-integrated on-chip peripherals waste silicon area, increase hardware attack surfaces, and generate software bloat if left unused. Engineers must actively disable these unused modules in software to prevent unnecessary power draw, adding overhead to the initialization sequence.

Managing Restrictive Vendor HALs vs. Bare-Metal Environments

A significant source of deployment friction in 2026 is vendor HAL bloat. Code generation tools like STM32Cube, MCUXpresso, and MPLAB Harmony often produce a "lowest common denominator HAL" designed to support an entire family of chips, which obscures the specialized hardware features of a specific MCU.

Pro Tip: When a vendor HAL is too restrictive, firmware teams are forced to create a "Frankenstein HAL"—mixing bloated vendor APIs with bare-metal register writes to achieve the necessary performance. To mitigate this, evaluate whether a vendor's ecosystem allows for a clean, bare-metal GCC/Make/VSCode environment before committing to their proprietary IDE.

Evaluating Deep Sleep Wake-Up Latency and Interrupt Reaction Time

Wake-up latency—the microsecond delay between a deep-sleep state and the execution of the first instruction—often dictates system power efficiency more than the theoretical minimum sleep current listed on a datasheet.

Theoretical Sleep Current vs. Actual Hardware Latency

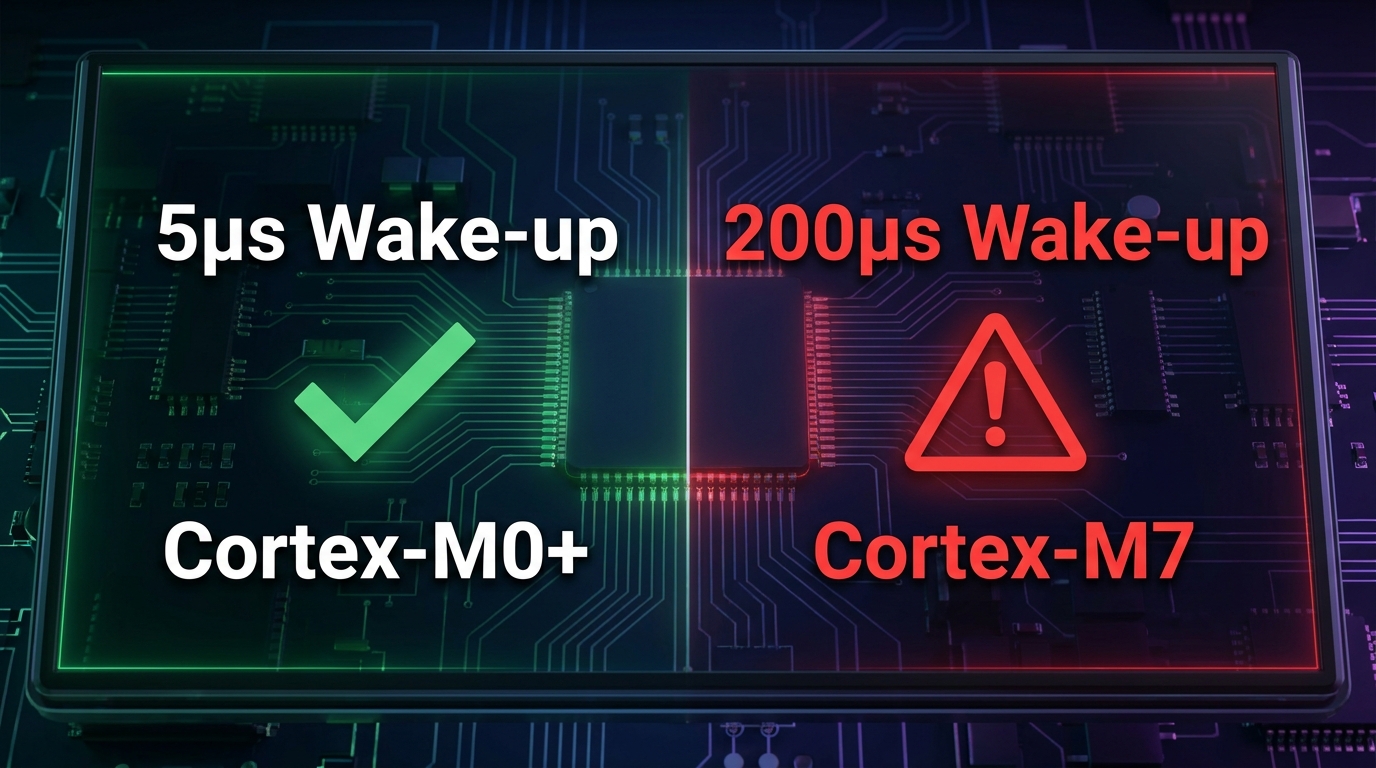

While many guides suggest "future-proofing" a battery-powered IoT device by selecting a high-performance core with an ultra-low deep-sleep rating, professional workflows actually require evaluating the wake-up lag. A cheaper Cortex-M0+ that can wake up and service an interrupt in 5µs will drastically outperform a premium Cortex-M7 that requires 200µs just to restore its clock trees and cache before executing code. The energy wasted during that 200µs wake-up lag completely negates the ultra-low 20nA sleep rating.

Implementing Tickless Mode in Modern RTOS Configurations

To maximize battery life, embedded systems developers utilize "tickless mode" within a Real-Time Operating System (RTOS). In a standard configuration, an RTOS wakes up every millisecond to process the system clock tick, draining power. Tickless mode allows the system to calculate the time until the next scheduled task, program a low-power timer, and enter deep sleep without waking for every system clock tick. The selected MCU must feature a reliable, low-power real-time clock (RTC) capable of triggering this precise wake-up sequence.

Top Microcontrollers for Continuous IoT Sensing and Wireless Connectivity

Continuous IoT sensing requires asymmetric multi-core architectures to handle background data acquisition, while wireless connectivity demands pre-certified modules and mature protocol stacks to minimize certification delays.

NXP MCX L Series: Asymmetric Dual-Domain Architecture

For continuous data acquisition, the NXP MCX L series (L14x/L25x) utilizes an asymmetric dual-core architecture featuring an Arm Cortex-M33 (up to 96 MHz) and an ultra-low-power Cortex-M0+ sense domain (up to 10 MHz). According to official specifications, this sense domain can operate at just 8µA/MHz while the main M33 core remains in deep sleep. This allows engineers to achieve continuous sensor thresholding without paying the energy penalty of waking the primary application core.

Nordic nRF52: Pre-Certified BLE Modules and Software Stability

The Nordic nRF52 remains the industry standard for Bluetooth Low Energy (BLE) applications due to its highly stable, mature software stack. In visual stress tests and hardware breakdowns, we observed the Fanstel BM832 pre-certified module, which visually guides developers away from designing bare-chip RF circuits. Utilizing pre-certified modules saves significant FCC/CE certification headaches.

The Steel-Man Standard: The nRF52 is an excellent choice for users who need rock-solid BLE connectivity and ultra-low transmit/receive currents. However, for projects that do not require Bluetooth, the nRF52 carries a premium price tag that makes it an inefficient choice for a general-purpose microcontroller.

Espressif ESP32-C6: Implementing Wi-Fi 6, Thread, and Zigbee

For 2026 IoT projects requiring modern networking protocols, visual hardware analyses explicitly highlight the ESP32-C6 as the specific RISC-V alternative needed for Wi-Fi 6, Thread, or Zigbee integration.

Counter-Intuitive Fact: Because the ESP32 ecosystem is highly accessible and inexpensive, engineers often default to it even when a project lacks wireless requirements. This is a critical error; the ESP32 series is power-hungry compared to standard ARM Cortex-M or dedicated low-power RISC-V chips, and using it unnecessarily will destroy a tight battery budget.

Top Microcontrollers for New Energy: Motor Control and Edge AI

New Energy applications, such as solar inverters and EV traction, require deterministic execution and high-resolution timers for Field Oriented Control (FOC), alongside dedicated neural processing units for edge AI workloads.

Deterministic Execution for Field Oriented Control: STM32G4 and dsPIC33

In digital power conversion and motor control, raw megahertz is secondary to deterministic execution. The STMicroelectronics STM32G4 series and Microchip’s dsPIC33 are optimized for tight ADC triggering. Specifically, the STM32G4 series includes a specialized High-Resolution Timer (HRTIM) capable of 184-picosecond resolution, driven by a hardware Delay-Locked Loop (DLL) operating between 100 and 170 MHz. This 184ps specification provides the superior determinism required for high-frequency FOC that general-purpose MCUs cannot match.

Migrating Control Systems to the STM32G Series

Many legacy industrial projects currently rely on the older STM32F series. Experts point out that the newer STM32G series is the cost-efficient evolution, offering similar capabilities but with lower power consumption and better pricing. This makes it the default professional choice for non-wireless control systems.

Accelerating Edge AI with the NXP i.MX RT700 Neural Processing Unit

The integration of dedicated hardware for machine learning has rendered software-only Cortex-M inference obsolete for complex tasks. The integrated eIQ Neutron Neural Processing Unit (NPU) in the NXP i.MX RT700 delivers up to 172x faster image classification and reduces energy per inference by up to 119x compared to running the same workloads on the Cortex-M33 alone. This allows smart meters to perform localized anomaly detection without draining the system battery.

Exploring Multi-Core Configurations and Open-Source RISC-V Alternatives

The transition toward open-source instruction sets and flexible multi-core designs allows firmware teams to mitigate supply chain risks and avoid architecture lock-in.

Raspberry Pi RP2350: Software-Based Core Switching and SRAM Allocation

The Raspberry Pi RP2350 features a unique dual-architecture design allowing developers to switch via software or OTP memory between dual Arm Cortex-M33 cores and dual open-source Hazard3 RISC-V cores (both running at 150MHz). In visual breakdowns of the architecture, specific allocation arrows demonstrate how its 520 KB of on-chip SRAM is utilized for "Buffers," "Logging," "Diagnostics," and "Future firmware growth." With 520 KB of SRAM, developers can allocate dedicated memory blocks to RTOS buffers, preventing the need for hardware redesigns later.

Component Bill of Materials: RP2350 External Flash Requirements

Despite its processing flexibility, the RP2350 lacks onboard flash memory. Engineers must include external flash memory in the bill of materials. While this prevents memory lock-in and allows for scalable storage, it adds a component to the PCB and slightly increases board routing complexity.

GigaDevice GD32V: Cost Reductions vs. Ecosystem Support Risks

The GigaDevice GD32V is utilized for ultra-cost-sensitive designs because its open-source RISC-V architecture eliminates ARM licensing fees, driving the unit cost down significantly. However, experts explicitly warn that its documentation quality and community support are limited. This chip is not designed for junior developers; it requires an experienced firmware team comfortable validating peripheral registers themselves.

Structured Decision Aid: 2026 MCU Architecture Selection Matrix

To streamline the selection process, use the following matrix to align project requirements with the appropriate silicon architecture.

| Primary Project Requirement | Recommended Architecture / Family | Key Engineering Advantage | Primary Trade-off |

|---|---|---|---|

| Continuous IoT Sensing | NXP MCX L Series | 8µA/MHz sense domain allows main core to sleep. | Requires managing asymmetric dual-core firmware. |

| Battery-Powered BLE | Nordic nRF52 (w/ Pre-certified Module) | Mature BLE stack; ultra-low TX/RX currents. | Premium unit price; inefficient for non-wireless tasks. |

| High-Frequency Motor Control | STM32G4 Series | 184ps HRTIM resolution for deterministic FOC. | Steeper learning curve for advanced timer configuration. |

| Edge AI / Anomaly Detection | NXP i.MX RT700 | NPU delivers 172x faster inference at 119x less energy. | High complexity; overkill for basic thresholding. |

| Architecture Evaluation | Raspberry Pi RP2350 | Software-switchable ARM Cortex-M33 and RISC-V cores. | Requires external flash memory on the BOM. |

Conclusion: Moving from Prototype to Production

Selecting the correct microcontroller in 2026 requires looking past top-line megahertz and theoretical sleep currents. For IoT and New Energy applications, the strategic winner is the MCU that minimizes deployment friction. Hardware engineers must prioritize architectures that offer rapid deep-sleep wake-up latencies, deterministic timer execution for motor control, and ecosystems that allow for bare-metal flexibility when vendor HALs become too restrictive. By factoring in tooling costs, documentation maturity, and the necessity of pre-certified modules, development teams can avoid the costly mistake of spinning boards for silicon that looks perfect on a datasheet but fails in production.

Frequently Asked Questions (FAQ)

Can I set up a bare-metal GCC/VSCode environment instead of using the vendor’s bloated IDE?

Yes. While vendors push proprietary IDEs (like STM32CubeIDE or MCUXpresso), most modern ARM Cortex-M and RISC-V microcontrollers can be configured using a standard GCC toolchain, Make/CMake, and VSCode. This approach prevents vendor lock-in and allows firmware teams to avoid bloated, auto-generated HAL code.

What is the actual 'wake-up time' from deep sleep for standard Cortex-M0+ MCUs?

A well-optimized Cortex-M0+ can typically wake from deep sleep and begin executing an interrupt service routine (ISR) in approximately 5 to 10 microseconds. This rapid reaction time makes it vastly superior for battery-powered event-driven systems compared to higher-end cores that may require 100µs to 200µs to restore clock trees.

Why should I migrate my legacy project from the STM32F series to the STM32G series?

The STM32G series is the modern, cost-efficient evolution of the STM32F line. It offers similar or improved peripheral capabilities (such as advanced analog features and high-resolution timers) but with significantly lower power consumption and a more competitive volume price point.

Which MCU ecosystem offers the most mature documentation without requiring restrictive NDAs?

For wireless applications, Nordic Semiconductor is widely recognized by the community for providing highly stable, well-documented software stacks (particularly for BLE) without hiding critical register details behind aggressive NDAs. For general-purpose ARM development, STMicroelectronics provides extensive, publicly available reference manuals.

Is the ESP32 series suitable for ultra-low-power, battery-operated IoT sensors?

Generally, no. While the ESP32 series (including the ESP32-C6) is excellent for Wi-Fi, Thread, and Zigbee applications, it is inherently power-hungry compared to dedicated low-power MCUs like the NXP MCX L series or standard Cortex-M0+ chips. Using an ESP32 for a device that does not require wireless connectivity will unnecessarily drain the battery budget.

Discovering New and Advanced Methodology for Determining the Dynamic Characterization of Wide Bandgap DevicesSaumitra Jagdale15 March 20242498

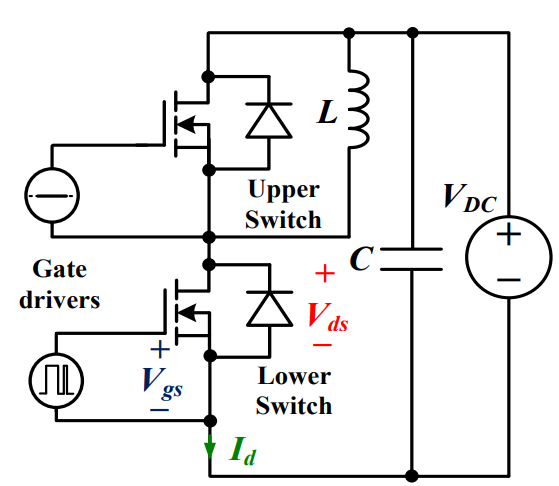

Discovering New and Advanced Methodology for Determining the Dynamic Characterization of Wide Bandgap DevicesSaumitra Jagdale15 March 20242498For a long era, silicon has stood out as the primary material for fabricating electronic devices due to its affordability, moderate efficiency, and performance capabilities. Despite its widespread use, silicon faces several limitations that render it unsuitable for applications involving high power and elevated temperatures. As technological advancements continue and the industry demands enhanced efficiency from devices, these limitations become increasingly vivid. In the quest for electronic devices that are more potent, efficient, and compact, wide bandgap materials are emerging as a dominant player. Their superiority over silicon in crucial aspects such as efficiency, higher junction temperatures, power density, thinner drift regions, and faster switching speeds positions them as the preferred materials for the future of power electronics.

Read More A Comprehensive Guide to FPGA Development BoardsUTMEL11 September 202515634

A Comprehensive Guide to FPGA Development BoardsUTMEL11 September 202515634This comprehensive guide will take you on a journey through the fascinating world of FPGA development boards. We’ll explore what they are, how they differ from microcontrollers, and most importantly, how to choose the perfect board for your needs. Whether you’re a seasoned engineer or a curious hobbyist, prepare to unlock new possibilities in hardware design and accelerate your projects. We’ll cover everything from budget-friendly options to specialized boards for image processing, delve into popular learning paths, and even provide insights into essential software like Vivado. By the end of this article, you’ll have a clear roadmap to navigate the FPGA landscape and make informed decisions for your next groundbreaking endeavor.

Read More Applications of FPGAs in Artificial Intelligence: A Comprehensive GuideUTMEL29 August 20253827

Applications of FPGAs in Artificial Intelligence: A Comprehensive GuideUTMEL29 August 20253827This comprehensive guide explores FPGAs as powerful AI accelerators that offer distinct advantages over traditional GPUs and CPUs. FPGAs provide reconfigurable hardware that can be customized for specific AI workloads, delivering superior energy efficiency, ultra-low latency, and deterministic performance—particularly valuable for edge AI applications. While GPUs excel at parallel processing for training, FPGAs shine in inference tasks through their adaptability and power optimization. The document covers practical implementation challenges, including development complexity and resource constraints, while highlighting solutions like High-Level Synthesis tools and vendor-specific AI development suites from Intel and AMD/Xilinx. Real-world applications span telecommunications, healthcare, autonomous vehicles, and financial services, demonstrating FPGAs' versatility in mission-critical systems requiring real-time processing and minimal power consumption.

Read More 800G Optical Transceivers: The Guide for AI Data CentersUTMEL24 December 20254527

800G Optical Transceivers: The Guide for AI Data CentersUTMEL24 December 20254527The complete guide to 800G Optical Transceiver standards (QSFP-DD vs. OSFP). Overcome supply shortages and scale your AI data center with Utmel Electronic.

Read More The 2026 Engineer’s Guide: Choosing the Right MCU for Your Next IoT & New Energy ProjectUTMEL30 April 202610

The 2026 Engineer’s Guide: Choosing the Right MCU for Your Next IoT & New Energy ProjectUTMEL30 April 202610A comprehensive comparison of 2026's leading MCUs from ST, NXP, and Microchip across power efficiency, processing performance, connectivity, and ecosystems to help engineers select the optimal chip for next-gen IoT and new energy projects.

Read More

Subscribe to Utmel !

![MOC3020VM]() MOC3020VM

MOC3020VMON Semiconductor

![HCS201T/SN]() HCS201T/SN

HCS201T/SNMicrochip Technology

![DLP6500BFYE]() DLP6500BFYE

DLP6500BFYETexas Instruments

![80HCPS1432CHMGI]() 80HCPS1432CHMGI

80HCPS1432CHMGIRenesas Electronics America Inc.

![MOC3082SVM]() MOC3082SVM

MOC3082SVMON Semiconductor

![DLP9500BFLN]() DLP9500BFLN

DLP9500BFLNTexas Instruments

![LTC3725EMSE#TRPBF]() LTC3725EMSE#TRPBF

LTC3725EMSE#TRPBFLinear Technology/Analog Devices

![MC68882RC50A]() MC68882RC50A

MC68882RC50ANXP USA Inc.

![LTC4213IDDB#TRMPBF]() LTC4213IDDB#TRMPBF

LTC4213IDDB#TRMPBFLinear Technology/Analog Devices

![FM31276-GTR]() FM31276-GTR

FM31276-GTRCypress Semiconductor Corp

Product

Product Brand

Brand Articles

Articles Tools

Tools