The Difference and Application of SPI, UART, I2C Communication

PROTOCOLS: UART - I2C - SPI - Serial communications #001

| Topics covered in this article: |

| Ⅰ. Serial VS Parallel |

| Ⅱ. SPI communication |

| Ⅲ. UART communication |

| Ⅳ. I²C communication |

| Ⅴ. Quick comparison & selection tips |

Communication between electronic devices is like human conversation—both sides need a shared “language.” These languages are communication protocols.

I’ve written independent guides on SPI, UART, and I²C before. This article compares and contrasts them and fixes a few common misconceptions from older write-ups.

Ⅰ. Serial VS Parallel

Digital data is represented by bits (0/1). Bits are transmitted as voltage level changes. Note: logic “low” and “high” levels depend on the logic family (e.g., 3.3 V CMOS, 1.8 V, 5 V TTL)—not all systems use 0 V/5 V.

Parallel communication sends multiple bits at once on multiple lines; serial sends bits sequentially on one line (per direction). Parallel can be faster over very short distances but scales poorly (more pins, skew, crosstalk). Serial links dominate modern designs for pin efficiency and signal integrity.

Ⅱ. SPI communication

SPI (Serial Peripheral Interface) is a synchronous, full-duplex serial bus. Unlike UART or I²C, SPI streams arbitrary numbers of bits continuously without start/stop framing or addressing overhead.

Roles & naming (2025 terminology): Many vendors now prefer controller/target over the legacy master/slave; similarly some use COPI/CIPO instead of MOSI/MISO. This article uses controller/target with MOSI/MISO noted for familiarity.

Signals (typical 4-wire): SCLK (clock, from controller), MOSI (controller→target), MISO (target→controller), and CS/SS (chip select, active-low per target).

Key characteristics

No inherent addressing—each target needs its own CS (or a decoder/expander).

Clock polarity/phase defined by mode (0–3); one bit is transferred per clock edge per direction.

Practical fan-out limited by signal integrity and loading on SCLK/CS lines.

Speed

SPI clocks commonly run from a few MHz up to tens of MHz (e.g., 10–50 MHz typical on many MCUs; higher on fast SoCs). Throughput is often far higher than I²C, not merely “~2×”.

Typical transaction

Controller configures mode/frequency and asserts the target’s CS low.

Clock runs; bytes/bits shift out on MOSI while response shifts in on MISO.

Controller deasserts CS to end the transfer (frame boundary).

Pros

Very high throughput; full-duplex.

Simple framing; low protocol overhead.

Flexible word sizes (not limited to 8-bit).

Cons

More pins/wires than I²C/UART (min. 4, plus one CS per target unless using expanders).

No built-in acknowledgment or error detection—must be handled at higher layers.

Cable length/fan-out limited by clocked single-ended lines.

Ⅲ. UART communication

UART (Universal Asynchronous Receiver/Transmitter) is a hardware block (often inside MCUs) that converts between parallel bytes and asynchronous serial frames on a TX/RX pair. It is a link layer, not a multi-drop bus protocol.

Because UART is asynchronous, there’s no shared clock line. Frames include start bit(s), data bits, optional parity, and stop bit(s). Popular formats: 8-N-1, 7-E-1, etc.

Baud rate tolerance (corrected)

For reliable links, the combined baud rate error between the two ends should generally be kept within about 2–3%; many designs aim for ≤2%. Some links can tolerate up to ~5% with margin; 10% is typically too high and risks framing errors, especially at higher baud rates.

Electrical levels

TTL/CMOS UART (0–VDD, e.g., 3.3 V) for on-board connections.

RS-232 uses ± voltages and inversion (via a transceiver).

RS-485 adds differential signaling and multi-drop support (not plain UART levels).

Pros

Only two data wires (TX/RX) for point-to-point.

No clock line; simple and well-understood.

Optional parity for basic error detection.

Cons

Point-to-point only at TTL levels (no native multi-drop without RS-485 or similar).

Lower throughput than high-speed SPI; framing overhead reduces efficiency.

Timing tolerance matters; clock mismatch causes framing errors.

Ⅳ. I²C communication

I²C was introduced by Philips (now NXP Semiconductors) and is a synchronous, two-wire, open-drain bus supporting multiple controllers and targets on the same two lines.

Lines: SDA (Serial Data) and SCL (Serial Clock). Correction: “SDA” stands for Serial Data (not “Serial Data Architecture”). Both lines require pull-up resistors; devices pull the line low to signal bits.

Frames & acknowledgments

START, 7-bit (or 10-bit) address + R/W bit, data bytes (8 bits each), and ACK/NACK after every byte, ending with STOP.

Clock stretching and bus arbitration enable multi-master operation.

Addresses (corrected)

With 7-bit addressing there are 128 codes, but several are reserved (general call, CBUS, 10-bit prefix, etc.). Usable device addresses are typically 112. 10-bit addressing expands the space (not commonly used in hobby-class parts).

Speeds (modes)

Standard-mode: 100 kHz

Fast-mode: 400 kHz

Fast-mode Plus: 1 MHz

High-speed mode: 3.4 MHz

Ultra-Fast mode: 5 MHz (write-only, limited use)

Actual achievable speed depends on bus capacitance and pull-ups.

Pull-ups (updated note)

Values like 4.7 kΩ are common examples, but the correct resistor depends on VDD, total bus capacitance, and required rise time from the I²C spec. For longer buses / higher speeds, use lower values (e.g., 2.2–3.3 kΩ) or active pull-ups.

Pros

Only two wires regardless of device count.

Built-in addressing and byte-level ACK/NACK.

Supports multi-master and multi-target on one bus.

Cons (corrected)

Slower than high-speed SPI; byte-oriented (8-bit) payloads.

Open-drain with pull-ups limits speed and cable length.

Hardware/driver handling is more complex than simple UART point-to-point.

Topologies

Single controller, multiple targets: Typical; ensure unique addresses (some devices allow pin-set address variants). Remember reserved address ranges.

Multiple controllers: Arbitration prevents collisions; devices must release the bus if they detect another controller driving a dominant ‘0’ while they output a ‘1’.

Ⅴ. Quick comparison & selection tips

| Feature | SPI | UART | I²C |

| Wires | 4+ (SCLK, MOSI/COPI, MISO/CIPO, CS per target) | 2 (TX, RX) | 2 (SDA, SCL + pull-ups) |

| Duplex | Full-duplex | Half-duplex per wire pair (separate TX/RX) | Half-duplex shared bus |

| Addressing | None (use CS/decoders) | None (point-to-point) | 7-bit/10-bit (≈112 usable in 7-bit) |

| Typical speed | ~1–50 MHz (MCU-class) | Up to a few Mbps (with good tolerance) | 100 kHz–3.4 MHz (5 MHz UFm write-only) |

| Error handling | App-level (no ACK) | Parity optional; framing checks | ACK/NACK per byte |

| Best for | High-speed sensors, displays, memory | Debug consoles, simple point links | Low-pin multi-device control/monitor |

Rules of thumb:

Need speed and continuous streaming? Choose SPI.

Need simple point-to-point or a console? Choose UART (mind baud accuracy).

Need many low/medium-speed peripherals on two pins? Choose I²C (mind pull-ups & addressing).

Change log & corrections (since 2021)

Clarified that logic levels vary by technology; not always 0/5 V.

Replaced/augmented master/slave with controller/target; noted MOSI/MISO vs COPI/CIPO naming.

SPI speed note updated: often far faster than I²C (not merely “~2×”).

UART tolerance corrected: recommended combined baud error ≈2–3% (10% is not appropriate).

I²C corrections: SDA = Serial Data (not “Architecture”); 7-bit usable addresses ≈112 due to reservations; added full speed-mode list; clarified pull-up sizing depends on bus capacitance and rise-time requirements.

Fixed I²C pros/cons (removed “Hardware is simpler than UART” and an unrelated UART line that mentioned “baud rates within 10%”).

1. What is the full name of SPI?

SPI, is the abbreviation of Serial Peripheral interface, a high-speed, full-duplex, synchronous communication bus.

2. What is the difference between UART and serial port?

UART is a serial port, but the serial port is not necessarily UART, it includes UART.

3. What is the maximum length of the I2C bus?

The maximum length of the I2C bus is: less than 200mm~300mm, which is related to the transmission speed and wiring, and the I2C repeater chip can be used to extend the distance.

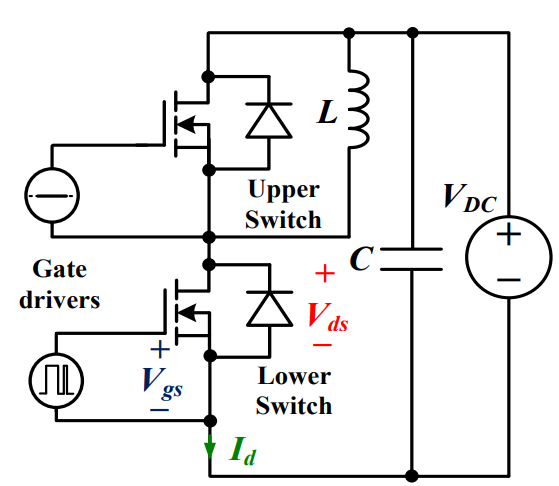

Discovering New and Advanced Methodology for Determining the Dynamic Characterization of Wide Bandgap DevicesSaumitra Jagdale15 March 20242486

Discovering New and Advanced Methodology for Determining the Dynamic Characterization of Wide Bandgap DevicesSaumitra Jagdale15 March 20242486For a long era, silicon has stood out as the primary material for fabricating electronic devices due to its affordability, moderate efficiency, and performance capabilities. Despite its widespread use, silicon faces several limitations that render it unsuitable for applications involving high power and elevated temperatures. As technological advancements continue and the industry demands enhanced efficiency from devices, these limitations become increasingly vivid. In the quest for electronic devices that are more potent, efficient, and compact, wide bandgap materials are emerging as a dominant player. Their superiority over silicon in crucial aspects such as efficiency, higher junction temperatures, power density, thinner drift regions, and faster switching speeds positions them as the preferred materials for the future of power electronics.

Read More A Comprehensive Guide to FPGA Development BoardsUTMEL11 September 202515224

A Comprehensive Guide to FPGA Development BoardsUTMEL11 September 202515224This comprehensive guide will take you on a journey through the fascinating world of FPGA development boards. We’ll explore what they are, how they differ from microcontrollers, and most importantly, how to choose the perfect board for your needs. Whether you’re a seasoned engineer or a curious hobbyist, prepare to unlock new possibilities in hardware design and accelerate your projects. We’ll cover everything from budget-friendly options to specialized boards for image processing, delve into popular learning paths, and even provide insights into essential software like Vivado. By the end of this article, you’ll have a clear roadmap to navigate the FPGA landscape and make informed decisions for your next groundbreaking endeavor.

Read More Applications of FPGAs in Artificial Intelligence: A Comprehensive GuideUTMEL29 August 20253708

Applications of FPGAs in Artificial Intelligence: A Comprehensive GuideUTMEL29 August 20253708This comprehensive guide explores FPGAs as powerful AI accelerators that offer distinct advantages over traditional GPUs and CPUs. FPGAs provide reconfigurable hardware that can be customized for specific AI workloads, delivering superior energy efficiency, ultra-low latency, and deterministic performance—particularly valuable for edge AI applications. While GPUs excel at parallel processing for training, FPGAs shine in inference tasks through their adaptability and power optimization. The document covers practical implementation challenges, including development complexity and resource constraints, while highlighting solutions like High-Level Synthesis tools and vendor-specific AI development suites from Intel and AMD/Xilinx. Real-world applications span telecommunications, healthcare, autonomous vehicles, and financial services, demonstrating FPGAs' versatility in mission-critical systems requiring real-time processing and minimal power consumption.

Read More 800G Optical Transceivers: The Guide for AI Data CentersUTMEL24 December 20254190

800G Optical Transceivers: The Guide for AI Data CentersUTMEL24 December 20254190The complete guide to 800G Optical Transceiver standards (QSFP-DD vs. OSFP). Overcome supply shortages and scale your AI data center with Utmel Electronic.

Read More Xilinx FPGAs: From Getting Started to Advanced Application DevelopmentUTMEL09 September 20254377

Xilinx FPGAs: From Getting Started to Advanced Application DevelopmentUTMEL09 September 20254377This guide is your comprehensive roadmap to understanding and mastering the world of Xilinx FPGA technology. From selecting your first board to deploying advanced AI applications, we'll cover everything you need to know to unlock the potential of these remarkable devices. The global FPGA market is on a significant growth trajectory, expected to expand from USD 8.37 billion in 2025 to USD 17.53 billion by 2035. This surge is fueled by the relentless demand for high-performance, adaptable computing in everything from 5G networks and data centers to autonomous vehicles and the Internet of Things (IoT). This guide will walk you through the key concepts, tools, and products in the Xilinx ecosystem, ensuring you're well-equipped to be a part of this technological revolution.

Read More

Subscribe to Utmel !

![FM31276-G]() FM31276-G

FM31276-GCypress Semiconductor Corp

![FOD4108TV]() FOD4108TV

FOD4108TVON Semiconductor

![TLP525GF]() TLP525GF

TLP525GFToshiba Semiconductor and Storage

![AD5560JBCZ-REEL]() AD5560JBCZ-REEL

AD5560JBCZ-REELAnalog Devices Inc.

![HCS515T/SL]() HCS515T/SL

HCS515T/SLMicrochip Technology

![STM802BDR]() STM802BDR

STM802BDRSTMicroelectronics

![AT88SC0104CA-PU]() AT88SC0104CA-PU

AT88SC0104CA-PUMicrochip Technology

![AT88SC1616C-SH-T]() AT88SC1616C-SH-T

AT88SC1616C-SH-TMicrochip Technology

![HCS101T-I/SN]() HCS101T-I/SN

HCS101T-I/SNMicrochip Technology

![MOC3163SM]() MOC3163SM

MOC3163SMON Semiconductor

Product

Product Brand

Brand Articles

Articles Tools

Tools