How are Integrated Circuits produced?

The Fabrication of Integrated Circuits

Catalog

I Introduction

Wafer manufacturing and chip manufacturing are two critical steps in the production of integrated circuits. Wafer manufacturing includes two major phases: ingot manufacturing and wafer processing. It can be subdivided into the following main processes: polysilicon → single crystal silicon → ingot growth → ingot cutting and inspection → outer diameter grinding → slicing → round edge grinding → surface grinding → etching → defect removal → polishing → (epitaxial growth → etching → defect removal) → cleaning → inspection → packaging. Chip manufacturing can be broadly divided into several key steps: Wafer Fabrication, Wafer Probe Testing, Packaging, Initial Test, and Final Test.

An integrated circuit is a miniature electronic device or component with specific circuit functions. The components needed in a circuit, such as transistors, resistors, capacitors, and inductors, are interconnected with wiring to create one or several small semiconductor wafers or dielectric substrates, which are then encapsulated in a package. All components have been integrated into a unified structure, making electronic components take a major step toward miniaturization, low power consumption, intelligence, and high reliability. It is represented in circuits by the letter "IC". The inventors of integrated circuits were Jack Kilby (germanium (Ge)-based integrated circuits) and Robert Noyce (silicon (Si)-based integrated circuits). Most applications in the semiconductor industry today are based on silicon integrated circuits.

The integrated circuit is a type of semiconductor device developed in the late 1950s and 1960s. It is manufactured through semiconductor fabrication processes such as oxidation, photolithography, diffusion, epitaxy, and metallization. These processes integrate semiconductors, resistors, capacitors, and other components onto a small piece of silicon to form a circuit with specific functions, which is then packaged in various forms including round shells, flat packages, or dual in-line packages. Integrated circuit technology encompasses both chip manufacturing technology and design technology, primarily reflected in processing equipment, fabrication processes, packaging and testing capabilities, mass production efficiency, and design innovation.

II Integrated Circuit Manufacturing Process

1. Wafer manufacturing (crystal growth-slicing-edge grinding-polishing-wrapping-shipping)

Figure 1 Crystal

Crystal Growth

Crystal growth requires a highly precise automated crystal pulling system. Quartz ore is refined using an electric arc furnace, chlorinated with hydrochloric acid, and distilled to produce high-purity polysilicon with a purity level of 99.999999999% (11 nines purity). A small amount of electroactive "dopants" such as arsenic, boron, phosphorus, or antimony are added to the refined polysilicon, and they are melted together in a high-temperature furnace. A long crystal cable is then used as a seed crystal and inserted into the molten polysilicon. The cable is rotated and slowly pulled upward. After cooling, a cylindrical single crystal silicon ingot, or silicon rod, is formed. This process is called "crystal growth" or the Czochralski process. Modern silicon ingots typically measure up to 3 feet in length and are available in diameters of 200mm (8 inches), 300mm (12 inches), and experimental 450mm formats. After the silicon ingot is ground, polished, and sliced, it becomes the basic raw material for manufacturing integrated circuits—silicon wafers.

Slicing / Edge Grinding / Surface Polishing

Figure 2 Ingot slicing

Slicing uses specialized wire saws or internal diameter blades to cut silicon ingots into thin wafers with precise geometries. The wafer surfaces and edges are then polished, ground, and cleaned. The sharp edges of newly cut wafers are rounded through edge grinding to remove rough scratches and surface impurities, resulting in nearly perfect silicon wafers. As of 2024-2025, 300mm wafers dominate production, accounting for approximately 70% of global wafer output, while 450mm wafer technology remains in the research and development stage due to cost and technical challenges.

Wrapping / Shipping

After wafer manufacturing is completed, specialized equipment is required to package and transport these nearly perfect silicon wafers. Wafer carriers provide semiconductor manufacturers with fast, consistent, and reliable wafer handling and storage solutions, protecting wafers from contamination and physical damage during transportation.

2. Deposition

Epitaxial Deposition

Figure 3 Wafers and epitaxial wafers

The epitaxial layer is often the first layer deposited on a semiconductor wafer. Most modern epitaxial growth depositions use low-pressure chemical vapor deposition (LPCVD) or molecular beam epitaxy (MBE) to grow silicon films on silicon substrates. The epitaxial layer, composed of ultra-pure silicon, acts as a buffer layer to prevent harmful impurities from diffusing into the silicon substrate. While bipolar processes generally required epitaxial layers, advanced CMOS technology may or may not use them depending on the specific application. Epitaxial layers are becoming increasingly important for 300mm wafer production as they can improve wafer quality by minimizing defect density.

Chemical Vapor Deposition (CVD)

Figure 4 Chemical Vapor Deposition

Chemical vapor deposition (CVD) is a technique that deposits materials on wafer surfaces by decomposing gas molecules. CVD produces many different types of films through thermal or plasma-enhanced processes. One common aspect is that the precursors are all in gaseous form. There are numerous CVD technologies, including thermal CVD, plasma-enhanced CVD (PECVD), atmospheric pressure CVD (APCVD), low-pressure CVD (LPCVD), high-density plasma CVD (HDPCVD), and atomic layer deposition (ALD), each suited to different applications in semiconductor manufacturing. ALD, in particular, has gained significant importance in advanced nodes below 10nm due to its atomic-level precision and conformality.

Physical Vapor Deposition (PVD)

Figure 5 Physical Vapor Deposition

Physical vapor deposition (PVD) methods are commonly used to prepare metal films for interconnects on wafers. While aluminum (Al) was historically the primary interconnect material, copper (Cu) has largely replaced it in modern processes. In PVD systems, target materials are bombarded with ions, causing atoms on the target surface to escape with specific energy and deposit onto the wafer surface. PVD is also used to deposit barrier layers, seed layers, and copper films for dual-damascene interconnect structures. As of 2024-2025, research is exploring ruthenium (Ru) and cobalt (Co) as potential replacements for copper interconnects at the most advanced nodes (below 2nm) where copper's resistivity becomes problematic at extremely small dimensions.

3. Photolithography

Figure 6 Photolithography

Photolithography is the process of printing chip circuit patterns onto wafers. It is the most critical step in integrated circuit manufacturing, accounting for approximately 35% of the overall manufacturing cost in the entire chip production process. Lithography is a key enabling technology that has allowed integrated circuits to follow Moore's Law, advancing from micrometers to deep sub-micron dimensions and into the nanometer era. Without continuous advancements in lithography technology, the progression of integrated circuits would be impossible.

The photolithography process transfers mask patterns to photoresist on the wafer surface. First, photoresist processing equipment spin-coats photoresist onto the wafer surface, then the wafer undergoes repeated exposure and development steps to form the required patterns. Process complexity is typically expressed by the number of mask layers required. Lithography can be classified by exposure method into contact, proximity, and projection types; by the number of lithographic planes into single-sided and double-sided alignment lithography; and by photoresist type into thin and thick photoresist processes. The general lithography process includes pre-treatment, spin coating, soft baking, alignment and exposure, development, and hard baking. Process steps can be adjusted based on specific requirements.

Advanced Lithography Technologies (2024-2025 Update): Extreme ultraviolet (EUV) lithography has become the industry standard for manufacturing advanced logic chips at 7nm and below. As of 2024-2025, High Numerical Aperture (High-NA) EUV lithography systems are being deployed, starting with Intel's installation of the first production-capable High-NA EUV system. High-NA EUV increases the numerical aperture from 0.33 to 0.55, enabling single-patterning of features down to approximately 8nm pitch, which is critical for future 2nm and 1nm nodes. These systems cost approximately $380-400 million each and represent the cutting edge of semiconductor manufacturing technology.

4. Etching

Figure 7 Etching

In the integrated circuit manufacturing process, after photoresist patterning through mask alignment, exposure, and development, or direct electron beam lithography, the desired pattern is created in the resist film. This pattern must then be accurately transferred to the underlying dielectric film (such as silicon oxide, silicon nitride, or polysilicon) or metal film. Etching selectively removes portions of the thin film not protected by the photoresist mask using chemical, physical, or combined chemical-physical methods, thereby creating a thin film pattern that precisely matches the photoresist pattern.

Plasma etching, also known as dry etching, is the ionization of reactive gases to form plasma under specific conditions. The plasma selectively removes material from the wafer, with the remaining material forming the chip pattern. Modern plasma etching techniques include reactive ion etching (RIE), inductively coupled plasma (ICP) etching, and atomic layer etching (ALE), which provides atomic-level precision for the most advanced nodes.

5. Ion Implantation

The wafer substrate is composed of pure silicon material, which is non-conductive or weakly conductive. To create conductivity in specific regions of the chip, small amounts of impurities must be precisely introduced into the wafer—typically arsenic, boron, and phosphorus. Doping can be accomplished through thermal diffusion in a furnace or by ion implantation. Advanced applications predominantly use ion implantation due to its superior precision and control. There are three main types of ion implantation: medium-current ion implantation for general doping, high-current/low-energy ion implantation for shallow junction formation, and high-energy ion implantation for deep well formation, each suited to different application requirements. Ion implantation offers advantages including precise dose control, excellent uniformity, low thermal budget, and the ability to implant through thin layers.

6. Thermal Processing

Thermal processing uses thermal energy to modify material properties and eliminate internal stresses within structures. The applied energy increases the vibration and diffusion of lattice atoms and defects, allowing atomic rearrangement. Thermal processing is performed after various deposition and implantation steps to change the mechanical and electrical properties of deposited films and to activate implanted dopants.

Currently, there are several key applications of thermal processing technology: One application uses ultra-low-k dielectrics to increase the hardness and mechanical stability of porous films, which is essential for reducing parasitic capacitance in advanced interconnects. Another uses high-stress nitride films to increase the toughness and tensile strength of deposited films, improving device performance through strain engineering. In UV-assisted thermal treatment reactors, plasma-enhanced chemical vapor deposition films undergo property changes through a combination of light and thermal energy. The ultraviolet treatment process in high-stress nitride films promotes bond rearrangement and improved film density, resulting in the high-stress levels required to enhance device performance. Rapid thermal processing (RTP) and rapid thermal annealing (RTA) are also critical for dopant activation while minimizing unwanted diffusion in advanced CMOS devices.

7. Chemical Mechanical Polishing (CMP)

One of the keys to advancing chip technology is the increasing number of layers per chip. As more layers are stacked on a chip, and the topography of each layer becomes more complex, the difficulty of lithographically patterning fine circuit features increases significantly. The CMP system uses a combination of polishing pads and chemical-mechanical abrasive slurries to selectively polish and planarize deposited layers. CMP applications include polysilicon planarization, pre-metal dielectric (PMD) planarization, interlayer dielectric (ILD) planarization, and tungsten planarization. CMP is an absolutely critical enabling technology for copper damascene and dual-damascene interconnect processes, which are standard in modern chip manufacturing. Advanced CMP processes must handle an increasing variety of materials including copper, cobalt, ruthenium, various low-k and ultra-low-k dielectrics, and barrier materials while maintaining excellent uniformity and minimal defectivity.

8. Wafer Metrology

In the chip manufacturing process, to ensure wafers are processed according to predetermined design requirements, extensive inspection and measurement must be performed, including critical dimension (CD) measurement of line widths on chips, film thickness measurement of each layer, surface topography measurement, overlay accuracy measurement, and electrical performance characterization at various stages.

With the continuous development of semiconductor processes and manufacturing technologies, these measurements have become indispensable for improving production yield and quality. In advanced processes using EUV lithography, copper damascene interconnects, and low-k dielectric materials, more sophisticated metrology equipment and novel measurement methods are required. Modern metrology must handle increasingly challenging requirements such as measuring features below 10nm, characterizing 3D structures like FinFETs and gate-all-around (GAA) transistors, and performing inline measurements at high throughput.

Metrology primarily includes three categories: optical inspection (using scatterometry, ellipsometry, and reflectometry), thin-film metrology (measuring thickness, composition, and stress), and critical dimension scanning electron microscopy (CD-SEM) for high-resolution dimensional measurements. An important development trend in wafer metrology is the integration of multiple measurement techniques in a single platform and the increasing use of artificial intelligence and machine learning for data analysis, defect classification, and process optimization.

9. Wafer Inspection (Particles and Defects)

Figure 8 Wafer Inspection System

Many steps in the wafer manufacturing process require contamination inspection for particles and defects, such as bare wafer inspection, equipment monitoring (using monitor wafers to detect particles deposited by process equipment), and inspection after CMP, CVD, PVD, and ion implantation. Typically, such inspections are performed before critical wafer processing steps or before photoresist layer exposure, which is referred to as unpatterned or patternless inspection.

Advanced inspection systems use optical techniques (brightfield and darkfield illumination), electron beam inspection, and increasingly, AI-powered defect detection algorithms to identify and classify defects with high sensitivity and throughput. As feature sizes shrink and process complexity increases, defect detection sensitivity must continuously improve, with modern systems capable of detecting particles and defects well below 20nm in size.

10. Wafer Probe Test

Wafer probe testing performs electrical testing of each die on the fabricated wafer. During testing, the wafer is secured on a vacuum chuck. Hair-thin probes make contact with every bond pad on each chip. The testing process verifies the electrical performance and circuit functionality of each die. Defective dies are marked with ink dots, and when the wafer is subsequently diced into individual chip units, the marked defective dies are identified and discarded. Data from probe testing can now be used through advanced analytics and yield management systems to help improve manufacturing yield and identify systematic process issues.

AI-Enhanced Testing (2024-2025): Artificial intelligence and machine learning are increasingly being integrated into wafer probe testing and final test processes. AI algorithms can predict potential failures, optimize test coverage, reduce test time while maintaining quality, and identify subtle patterns in test data that indicate process drift or systematic defects. This represents a significant advancement in semiconductor testing efficiency and effectiveness.

11. Packaging (Assembly & Packaging)

Figure 9 Wafer package

Packaging technology has developed rapidly in recent years, driven primarily by: (a) The increasing complexity of chips: the number of transistors contained in chips has increased dramatically, and pin counts have also risen substantially. New packaging technologies are needed to meet these demands. (b) Miniaturization of electronic products: Today's electronic products require compact size, powerful functionality, and low power consumption, which translates to higher requirements for interconnect density, and packaging forms must adapt to these changes. (c) Performance requirements: As chips become more powerful, especially for AI and high-performance computing applications, packaging must address thermal management, power delivery, and signal integrity challenges.

Individual chips are separated from the wafer through dicing and then packaged to enable the chips to be eventually mounted on printed circuit boards (PCBs). Required equipment includes wafer dicing machines (typically using diamond blade saws or laser dicing), die-attach machines (which mount chips into lead frames or substrates), and wire bonders (responsible for connecting chips to lead frames or substrates using technologies such as gold wire bonding, copper wire bonding, or aluminum wire bonding). Different wire bonding materials have distinct advantages and disadvantages: gold (Au) offers excellent reliability but higher cost, aluminum (Al) provides good bonding characteristics at lower cost, and copper (Cu) offers a balance of performance and cost-effectiveness. With the emergence of multi-layer packaging, 3D stacking, and even advanced 3D packaging applications, the demand for ultra-thin wafers (down to 50μm or less) is also increasing significantly.

Advanced Packaging Technologies (2024-2025): The packaging industry has undergone a revolutionary transformation. Advanced packaging technologies now include:

Chiplet Technology: Multiple smaller dies (chiplets) are integrated into a single package, enabling heterogeneous integration where different chiplets can be manufactured using optimal process nodes and technologies. This approach improves yields and reduces costs while enabling system-level optimization.

2.5D Packaging: Dies are mounted side-by-side on a silicon interposer, enabling high-bandwidth, low-latency communication between chips. This technology is widely used in high-performance computing and AI accelerators.

3D Packaging and Through-Silicon Vias (TSVs): Multiple dies are stacked vertically and connected using TSVs—vertical electrical connections passing through silicon—enabling the highest interconnect density and shortest interconnect lengths. Technologies like TSMC's SoIC (System on Integrated Chips) and Intel's Foveros represent the state-of-the-art in 3D integration.

Hybrid Bonding: A wafer-to-wafer or die-to-wafer bonding technique that creates direct copper-to-copper and dielectric-to-dielectric bonds without solder bumps, enabling extremely fine-pitch connections (below 10μm pitch) and superior electrical performance.

Fan-Out Wafer-Level Packaging (FOWLP): Interconnects fan out beyond the die area, enabling higher I/O density and improved thermal and electrical performance in a compact form factor.

These advanced packaging technologies are critical for continuing performance improvements as traditional transistor scaling becomes increasingly challenging and expensive. The packaging industry is projected to grow significantly, with advanced packaging representing an increasing share of overall semiconductor packaging revenue.

12. Final Test

Because final chip yield cannot reach 100%, comprehensive testing of packaged chips becomes critically important. How to identify high-performance chips and how to test them quickly and thoroughly are paramount concerns. Considering that each chip must be tested individually, fabrication facilities must carefully balance test coverage, quality, and cost. This has driven the development of new generations of test equipment with more comprehensive test capabilities, lower per-unit costs, and faster test speeds.

Final test typically includes multiple test categories: functional testing (verifying correct circuit operation), parametric testing (measuring electrical characteristics such as voltage, current, and timing), burn-in testing (accelerated life testing under elevated temperature and voltage to identify early failures), and system-level testing (verifying performance in application-relevant conditions). Advanced test strategies increasingly leverage statistical methods, machine learning algorithms, and adaptive testing to optimize test efficiency while maintaining or improving quality levels. For complex chips such as microprocessors and AI accelerators, test development and execution can represent a significant portion of overall product cost.

III Emerging Technologies and Future Trends (2024-2025)

Gate-All-Around (GAA) Transistors

Gate-all-around field-effect transistors (GAA FETs), also known as nanosheet transistors or nanowire transistors, represent the next evolution beyond FinFET technology. Unlike FinFETs where the gate wraps around three sides of the channel, GAA transistors feature gates that completely surround the channel on all four sides, providing superior electrostatic control. This architecture enables continued transistor scaling below 3nm nodes while improving performance and reducing power consumption. Samsung began mass production of GAA transistors at their 3nm node in 2022, and other major manufacturers including TSMC and Intel are implementing GAA technology at their most advanced nodes. GAA technology offers benefits including reduced short-channel effects, improved drive current, better subthreshold slope, and greater design flexibility through adjustable channel width.

Artificial Intelligence in Semiconductor Manufacturing

Artificial intelligence and machine learning are transforming semiconductor manufacturing across multiple domains. AI applications in semiconductor fabrication include:

Yield Enhancement: ML algorithms analyze vast amounts of manufacturing data to identify patterns correlating with yield loss, enabling predictive maintenance and process optimization.

Defect Detection and Classification: Deep learning models can detect and classify defects in wafer inspection with superhuman accuracy and speed.

Process Control: AI-driven advanced process control (APC) systems can make real-time adjustments to maintain optimal process conditions.

Design Optimization: AI tools assist in chip design, layout optimization, and design rule checking, significantly reducing design time and improving performance.

Equipment Health Monitoring: Predictive maintenance algorithms analyze equipment sensor data to predict failures before they occur, minimizing downtime.

The semiconductor industry is investing heavily in AI capabilities, with the market for AI chips themselves expected to exceed $150 billion in 2025, driving a virtuous cycle where AI improves semiconductor manufacturing while advanced semiconductors enable more powerful AI systems.

Sustainable Manufacturing Initiatives

Environmental sustainability has become a critical focus for the semiconductor industry. Modern fabs consume enormous amounts of water, energy, and chemicals. Industry initiatives addressing sustainability include:

Water Recycling: Advanced water treatment and recycling systems can reclaim and reuse over 90% of ultra-pure water used in fabrication.

Energy Efficiency: Implementing renewable energy sources, improving equipment energy efficiency, and optimizing facility operations to reduce carbon footprint.

Chemical Management: Developing alternative chemistries with lower environmental impact and implementing closed-loop chemical delivery systems.

Circular Economy: Recycling and recovering valuable materials including silicon, precious metals, and rare earth elements from manufacturing waste and end-of-life products.

Major semiconductor companies have announced ambitious carbon neutrality targets, with many aiming for net-zero emissions by 2040-2050.

Article Update Information:

Last Updated: October 2025

Original Publication: 2020

Major Updates Include:

Updated wafer size statistics and 300mm wafer production dominance (70% of global output as of 2024)

Clarification that 450mm wafer technology remains in R&D stage due to economic and technical challenges

Added comprehensive information on High-NA EUV lithography deployment (2024-2025)

Included section on Gate-All-Around (GAA) transistor technology for 3nm and below nodes

Expanded advanced packaging section with chiplet technology, 2.5D/3D packaging, hybrid bonding, and FOWLP

Added information on alternative interconnect metals (ruthenium, cobalt) for sub-2nm nodes

Included atomic layer deposition (ALD) as a critical deposition technique for advanced nodes

Added section on AI/ML applications in semiconductor manufacturing and testing

Included new section on sustainable manufacturing initiatives and environmental considerations

Corrected spelling and grammatical errors throughout the document

Updated terminology and technical descriptions to reflect current industry standards

Added context on industry market size: global semiconductor sales projected at $701 billion in 2025

Sources: Information updated based on industry reports from SEMI, Deloitte Global Semiconductor Outlook 2025, ASML High-NA EUV documentation, and recent semiconductor industry publications and research papers.

Recommended Articles:

What is an integrated circuit and how are they made?

Integrated circuit (IC), also called microelectronic circuit, microchip, or chip, an assembly of electronic components, fabricated as a single unit.

How does an integrated circuit work?

Integrated circuits are a combination of diodes, microprocessors, and transistors in a minimized form on a wafer made of silicon. Transistors – These components are used to store voltages or circuit stabilizer. They can be utilized to amplify the given signal and used as switches working in digital circuits.

How long does it take to make an integrated circuit?

Silicon is almost always used, but various compound semiconductors are used for specialized applications. The entire manufacturing process, from start to packaged chips ready for shipment, takes six to eight weeks and is performed in highly specialized semiconductor fabrication plants, also called foundries or fabs.

What are the benefits of integrated circuits?

The advantages of the integrated circuits include the following. Small size. Power consumption is less. Reliability. Less cost. Less weight. Replacement can be done very easily. More consistent. Improved operating speed & performance.

Why are integrated circuits used?

The advantages of Integrated Circuits are: Very small size: Hundred times smaller than the discrete circuits. Lesser weight: As large number of components can be packed into a single chip, weight is reduced.

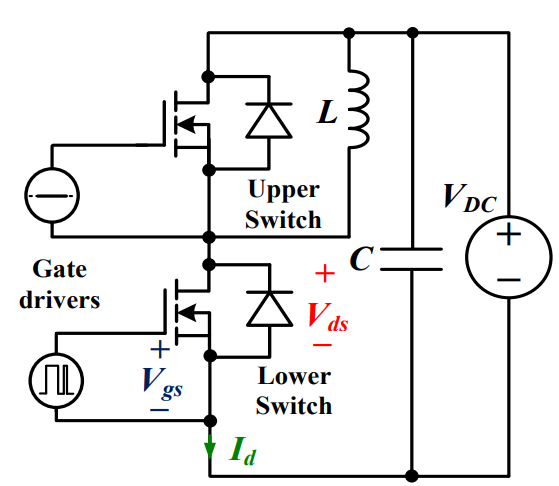

Discovering New and Advanced Methodology for Determining the Dynamic Characterization of Wide Bandgap DevicesSaumitra Jagdale15 March 20242454

Discovering New and Advanced Methodology for Determining the Dynamic Characterization of Wide Bandgap DevicesSaumitra Jagdale15 March 20242454For a long era, silicon has stood out as the primary material for fabricating electronic devices due to its affordability, moderate efficiency, and performance capabilities. Despite its widespread use, silicon faces several limitations that render it unsuitable for applications involving high power and elevated temperatures. As technological advancements continue and the industry demands enhanced efficiency from devices, these limitations become increasingly vivid. In the quest for electronic devices that are more potent, efficient, and compact, wide bandgap materials are emerging as a dominant player. Their superiority over silicon in crucial aspects such as efficiency, higher junction temperatures, power density, thinner drift regions, and faster switching speeds positions them as the preferred materials for the future of power electronics.

Read More A Comprehensive Guide to FPGA Development BoardsUTMEL11 September 202513975

A Comprehensive Guide to FPGA Development BoardsUTMEL11 September 202513975This comprehensive guide will take you on a journey through the fascinating world of FPGA development boards. We’ll explore what they are, how they differ from microcontrollers, and most importantly, how to choose the perfect board for your needs. Whether you’re a seasoned engineer or a curious hobbyist, prepare to unlock new possibilities in hardware design and accelerate your projects. We’ll cover everything from budget-friendly options to specialized boards for image processing, delve into popular learning paths, and even provide insights into essential software like Vivado. By the end of this article, you’ll have a clear roadmap to navigate the FPGA landscape and make informed decisions for your next groundbreaking endeavor.

Read More Applications of FPGAs in Artificial Intelligence: A Comprehensive GuideUTMEL29 August 20253468

Applications of FPGAs in Artificial Intelligence: A Comprehensive GuideUTMEL29 August 20253468This comprehensive guide explores FPGAs as powerful AI accelerators that offer distinct advantages over traditional GPUs and CPUs. FPGAs provide reconfigurable hardware that can be customized for specific AI workloads, delivering superior energy efficiency, ultra-low latency, and deterministic performance—particularly valuable for edge AI applications. While GPUs excel at parallel processing for training, FPGAs shine in inference tasks through their adaptability and power optimization. The document covers practical implementation challenges, including development complexity and resource constraints, while highlighting solutions like High-Level Synthesis tools and vendor-specific AI development suites from Intel and AMD/Xilinx. Real-world applications span telecommunications, healthcare, autonomous vehicles, and financial services, demonstrating FPGAs' versatility in mission-critical systems requiring real-time processing and minimal power consumption.

Read More 800G Optical Transceivers: The Guide for AI Data CentersUTMEL24 December 20253474

800G Optical Transceivers: The Guide for AI Data CentersUTMEL24 December 20253474The complete guide to 800G Optical Transceiver standards (QSFP-DD vs. OSFP). Overcome supply shortages and scale your AI data center with Utmel Electronic.

Read More Xilinx FPGAs: From Getting Started to Advanced Application DevelopmentUTMEL09 September 20254189

Xilinx FPGAs: From Getting Started to Advanced Application DevelopmentUTMEL09 September 20254189This guide is your comprehensive roadmap to understanding and mastering the world of Xilinx FPGA technology. From selecting your first board to deploying advanced AI applications, we'll cover everything you need to know to unlock the potential of these remarkable devices. The global FPGA market is on a significant growth trajectory, expected to expand from USD 8.37 billion in 2025 to USD 17.53 billion by 2035. This surge is fueled by the relentless demand for high-performance, adaptable computing in everything from 5G networks and data centers to autonomous vehicles and the Internet of Things (IoT). This guide will walk you through the key concepts, tools, and products in the Xilinx ecosystem, ensuring you're well-equipped to be a part of this technological revolution.

Read More

Subscribe to Utmel !

![MOC3023SR2VM]() MOC3023SR2VM

MOC3023SR2VMON Semiconductor

![ATECC608A-SSHDA-B]() ATECC608A-SSHDA-B

ATECC608A-SSHDA-BMicrochip Technology

![HCS300-I/SN]() HCS300-I/SN

HCS300-I/SNMicrochip Technology

![ATECC508A-SSHDA-T]() ATECC508A-SSHDA-T

ATECC508A-SSHDA-TMicrochip Technology

![KSZ8995X]() KSZ8995X

KSZ8995XMicrochip Technology

![ATECC508A-MAHDA-S]() ATECC508A-MAHDA-S

ATECC508A-MAHDA-SMicrochip Technology

![HCS200-I/SN]() HCS200-I/SN

HCS200-I/SNMicrochip Technology

![AT88SC0404CA-PU]() AT88SC0404CA-PU

AT88SC0404CA-PUMicrochip Technology

![KSZ8999]() KSZ8999

KSZ8999Microchip Technology

![MOC3052SR2M]() MOC3052SR2M

MOC3052SR2MON Semiconductor

Product

Product Brand

Brand Articles

Articles Tools

Tools