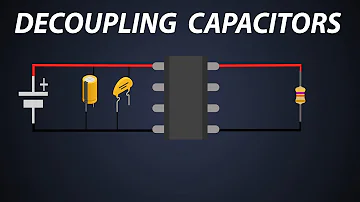

What is a Decoupling Capacitor?

What are the Decoupling capacitors?

Table of Contents

I. Introduction

Decoupling capacitors are fundamental components in modern electronic circuits, playing a crucial role in ensuring power integrity and signal stability. They act as local energy reservoirs, supplying instantaneous current to active devices and filtering out high-frequency noise from the power supply rails. As electronic systems become faster and more complex, with data rates pushing into the gigahertz range for standards like DDR5 and PCIe 6.0, the role of decoupling has evolved from a simple rule-of-thumb to a critical aspect of high-speed PCB design. This article provides a comprehensive overview of decoupling capacitors, covering their function, selection, and placement, with updated information and best practices for today's demanding applications.

In any circuit, the power distribution network (PDN) is not ideal. The traces and power planes have parasitic inductance and resistance, which impede the flow of current. When an integrated circuit (IC) switches its state, it demands a sudden surge of current (a high dI/dt). Due to the PDN impedance, this current surge can cause a localized voltage drop, or "ripple," on the power rail. If this voltage drop is significant enough, it can cause the IC to malfunction. Decoupling capacitors, placed close to the IC's power pins, provide a low-impedance path for this high-frequency current, effectively "decoupling" the IC from the noisy power supply.

II. The Dual Function of Decoupling Capacitors

Decoupling capacitors serve two primary, interconnected functions in a circuit's Power Distribution Network (PDN): providing a local source of charge to meet the high-frequency current demands of active devices, and shunting high-frequency noise to ground.

1. A Local Energy Source for High-Frequency Demands

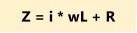

Modern digital ICs, like microcontrollers and FPGAs, have rapidly changing current demands. When transistors inside the chip switch, they draw a large amount of current in a very short time (a high dI/dt). The main power supply is often physically far from the IC, and the traces connecting them have parasitic inductance. This inductance resists fast changes in current, leading to a voltage drop (V = L × dI/dt) at the IC's power pins.

The decoupling capacitor acts as a miniature, local energy reservoir right next to the IC. It can supply the required transient current much faster than the main power supply can. You can think of the main power supply as a large reservoir and the decoupling capacitor as a water tower next to a building. The water tower (capacitor) can quickly supply water (charge) during peak demand, while the reservoir (power supply) refills the tower at a slower, steadier rate. This prevents the building's water pressure (voltage) from dropping.

2. Shunting High-Frequency Noise

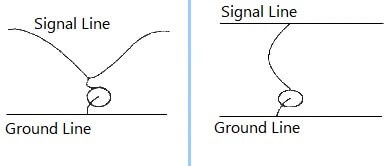

Because capacitors have low impedance at high frequencies, they provide an attractive path for high-frequency noise to flow to the ground plane, rather than propagating through the power distribution network and interfering with other components. The switching action of the IC itself is a major source of this high-frequency noise. By placing a decoupling capacitor directly between the IC's power and ground pins, we create a small, low-inductance loop that effectively contains and shunts this switching noise to ground, preventing it from polluting the rest of the circuit.

III. Bypass vs. Decoupling: A Clarification of Terms

In the world of electronics, the terms "bypass capacitor" and "decoupling capacitor" are often used interchangeably, which can be a source of confusion. While both serve to suppress noise and stabilize voltage, their names hint at a subtle difference in their intended function and historical application.

1. The Role of a Bypass Capacitor

A bypass capacitor provides a low-impedance path to ground for high-frequency noise, effectively "bypassing" it around a component or circuit that you want to protect from that noise. It's typically used to filter noise from power supply lines, shunting the unwanted AC components to ground and leaving a cleaner DC voltage.

2. The Modern View: One System, Different Roles

Historically, a distinction was made where bypass capacitors filtered incoming noise, while decoupling capacitors filtered outgoing noise from a switching IC. However, in modern high-speed design, this distinction is less relevant. It's more accurate to view all these capacitors as part of a comprehensive Power Distribution Network (PDN) strategy.

The key difference lies in their placement and primary purpose:

Decoupling Capacitor: Placed as close as possible to an IC's power and ground pins. Its main job is to supply the instantaneous switching current required by the IC and to contain the high-frequency noise generated by the IC in a small, low-inductance loop. It decouples the IC from the rest of the PDN.

Bypass Capacitor: This term is often used more generally for capacitors placed elsewhere on the board, such as at the entry point of the main power supply, to filter out noise from the power source. These are often larger "bulk" capacitors.

Essentially, a decoupling capacitor is a specific type of bypass capacitor, optimized for a particular location and function. Both contribute to the overall goal of maintaining a low-impedance PDN across a wide range of frequencies.

IV. From Simple Formulas to Target Impedance

Calculating the required decoupling capacitance has evolved from simple formulas to a more sophisticated approach based on the concept of target impedance. While older methods can provide a rough estimate, a modern Power Distribution Network (PDN) requires a more rigorous, frequency-domain analysis to ensure power integrity for high-speed devices.

1. The Traditional Calculation (A Starting Point)

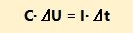

A common formula to estimate the required capacitance is based on the charge required during a transient event:

C = (Itransient × Δt) / ΔVripple

Where:

C is the capacitance.

Itransient is the maximum transient current required by the IC.

Δt is the duration of the transient event.

ΔVripple is the maximum allowable voltage drop (ripple) on the power rail.

While this formula is a good starting point for understanding the relationship between current, time, and voltage, it oversimplifies the problem. It treats the capacitor as an ideal component and doesn't account for the frequency-dependent nature of the PDN, including the critical effects of parasitic inductance (ESL) and resistance (ESR).

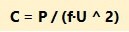

2. The Modern Approach: Target Impedance

The modern approach to PDN design focuses on maintaining the PDN impedance below a specific target impedance (Ztarget) across a wide frequency range. The target impedance is determined by the maximum allowable voltage ripple and the maximum transient current draw of the IC.

Ztarget = ΔVripple / Itransient

For example, if a 1.0V power rail has a maximum allowable ripple of 5% (50mV) and the IC can draw a transient current of 2A, the target impedance would be:

Ztarget = 0.050V / 2A = 0.025Ω (25mΩ)

The goal of the PDN design is then to create a network of power planes and decoupling capacitors that keeps the impedance below this 25mΩ target from DC up to the maximum frequency of interest (determined by the signal rise times).

Important Note: This approach requires specialized PDN analysis tools that can simulate the impedance profile of the entire network, including the PCB planes, capacitor models (with their ESR and ESL), and mounting inductance. This allows engineers to strategically select and place capacitors of different values to control the impedance at different frequencies, ensuring stable power delivery for even the most demanding high-speed components.

V. Selection and Layout of PCB Decoupling Capacitors: A Modern Perspective

The selection and placement of decoupling capacitors have evolved significantly from a set of simple rules to a nuanced engineering discipline. While the old adages of "place a 0.1µF capacitor on every power pin" served well for older logic families, they are insufficient for today's high-speed, high-density designs. A successful strategy relies on understanding the interplay between capacitor values, their physical characteristics (ESL, ESR), and the layout of the entire Power Distribution Network (PDN), especially the power and ground planes.

1. Capacitor Selection for a Wideband PDN

The goal is to achieve a low PDN impedance across a broad frequency spectrum, from DC to several hundred megahertz or even gigahertz. No single capacitor can achieve this. A combination of different capacitor types and values is required:

Bulk Capacitors (Low-Frequency): Typically in the range of 10µF to 100µF, these are usually tantalum or electrolytic capacitors. They are placed at the power entry point of the PCB and serve as large charge reservoirs, supplying current for low-frequency load changes (up to a few hundred kHz). Their high ESR and ESL make them ineffective at higher frequencies.

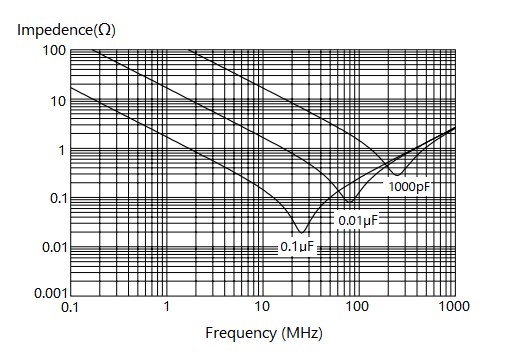

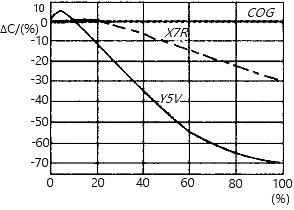

Ceramic Capacitors (Mid-to-High Frequency): Multilayer Ceramic Capacitors (MLCCs) are the workhorses of decoupling. They come in a range of values (e.g., 0.01µF, 0.1µF, 1µF, 10µF) and provide low impedance in the 1MHz to 500MHz range. It's common to use a parallel combination of different values (e.g., 10µF, 1µF, and 0.1µF) to create a broader low-impedance profile. However, care must be taken to avoid anti-resonance peaks where the parallel combination creates a high impedance at certain frequencies.

High-Frequency Capacitors: For frequencies above a few hundred MHz, the capacitor's parasitic inductance (ESL) becomes the dominant factor. The physical size of the capacitor is more important than its capacitance value. Smaller packages like 0402 or 0201 have lower ESL and are more effective at these frequencies. Values are typically smaller, from 1nF to 100nF.

2. The Critical Role of PCB Layout

Recent research and industry best practices have shown that the PCB layout, particularly the design of the power and ground planes, is more critical than the exact placement of individual capacitors.

The Power of Planes

A pair of closely spaced power and ground planes (e.g., 4 mils or 0.1mm apart or less) creates a very effective, low-inductance, parallel-plate capacitor. This "plane capacitance" is the most important element for high-frequency decoupling. If your PCB has tightly coupled planes, the need to place capacitors directly adjacent to every power pin is significantly reduced. The plane itself provides the immediate charge.

Modern Placement Strategy

Minimize Inductance in the Mounting Path: The goal is to minimize the total inductance from the capacitor to the IC's power and ground pins. This loop includes the capacitor itself, its pads, the traces to the vias, the vias themselves, and the connection from the vias to the IC's solder balls. The shortest path is the best path.

Placement on the Opposite Side: For dense BGAs, one of the most effective strategies is to place the decoupling capacitors on the opposite side of the PCB, directly beneath the IC's power pins. The capacitor and the IC can then share the same vias, creating a very short, low-inductance path.

Distribute Capacitors: Rather than crowding all capacitors around a single chip (which can be impossible with large BGAs), distribute them across the board. This improves overall PDN stability and is effective when you have well-designed power planes.

Prioritize Manufacturability: As highlighted by industry experts, capacitor placement must be practical. Avoid placing capacitors in locations that make assembly, inspection, or rework difficult or impossible, such as directly under a large BGA where they are inaccessible.

3. The Importance of PDN Simulation

Ultimately, the only way to be certain of your PDN performance is to simulate it. Modern EDA tools (from vendors like Cadence, Siemens, and Altium) include Power Integrity (PI) simulation capabilities. These tools allow you to import your PCB layout, along with accurate models for your capacitors, and analyze the PDN impedance versus frequency. This allows you to identify potential issues, like high-impedance peaks from anti-resonance, and optimize your capacitor selection and placement before fabrication, saving costly board respins.

VI. Frequently Asked Questions (FAQ)

Q1: Is the 0.1µF capacitor still a good default choice?

While the 0.1µF (or 100nF) capacitor has been a staple for decades, it is no longer a one-size-fits-all solution. For modern high-speed circuits, its effectiveness depends on the specific frequency requirements. It's often part of a larger strategy that includes multiple capacitor values. Relying solely on 0.1µF without proper analysis is an outdated practice. The focus should be on achieving a low target impedance across the required frequency band, which often requires a combination of capacitors (e.g., 10µF, 1µF, 0.1µF, and 0.01µF) and good plane design.

Q2: Should I place capacitors on the top or bottom side of the PCB?

For surface-mount devices, especially large Ball Grid Arrays (BGAs), placing decoupling capacitors on the bottom side of the PCB directly under the component's power pins is often the most effective strategy. This allows for the shortest possible connection path through vias, minimizing parasitic inductance. However, the primary goal is always to minimize the inductance loop, regardless of which side the capacitor is on.

Q3: How many decoupling capacitors do I need for my IC?

This depends entirely on the IC's requirements. Always consult the manufacturer's datasheet and any available design guidelines. For complex devices like FPGAs and processors, manufacturers provide detailed recommendations and often require a Power Integrity simulation to validate the design. The number of capacitors is less important than achieving the target PDN impedance.

Update Information: This article was originally published in 2020 and has been updated in October 2025 to reflect the latest industry best practices, technological advancements in capacitor technology, and the modern approach to Power Distribution Network (PDN) design for high-speed digital circuits. The core principles remain the same, but the emphasis has shifted from simple rules of thumb to a more analytical, simulation-based approach focused on achieving a target impedance.

Updating and Optimizing a 2020 Blog Post - Manus

1.What is the purpose of decoupling capacitor?

Decoupling capacitors are used to filter out voltage spikes and pass through only the DC component of the signal. The idea is to use a capacitor in such a way that it shunts, or absorbs the noise making the DC signal as smooth as possible.

2.Are decoupling capacitors necessary?

Using a properly connected decoupling capacitor can save you a lot of trouble. Even if your circuit works on the bench without decoupling, it could have issues when you go into production from process variation and other real world influences.

3.What is the difference between decoupling and bypass capacitor?

Some of the few noticeable difference between the bypass capacitor and decoupling capacitors are, the bypass capacitor is designed to shunt the noise signals where as the decoupling capacitors are designed to smoothen the signal by stabilizing the distorted signal.

4.Where should decoupling capacitors be placed?

Decoupling capacitors should be placed as close as possible to the source for the signal being decoupled. This means at the pin for ICs and near the connector for input and out signals. To remove LF transients from input and output signals, the capacitor should be placed in series with the trace.

5.How do you size a decoupling capacitor?

The general rule is to select the bulk capacitor value is to select at least ten times the total decoupling capacitance. For the core voltage, 10 × (total capacitance) = 0.39 μF. For the I/O voltage, 10 × (total capacitance) = 0.84 μF.

What is Feedthrough Capacitor?UTMEL06 November 202140441

What is Feedthrough Capacitor?UTMEL06 November 202140441Hello, everyone. I am Rose. Today I will introduce the feedthrough capacitor to you. The feedthrough capacitor is a three-terminal capacitor that is used to reduce high frequencies. The feedthrough capacitor, unlike regular three-terminal capacitors, is directly installed on the metal panel, resulting in a lower grounding inductance and a negligible effect on the lead inductance.

Read More Detailed Explanation About Twenty Kinds of CapacitorUTMEL08 November 20218926

Detailed Explanation About Twenty Kinds of CapacitorUTMEL08 November 20218926Hello everyone, I am Rose. Today I will introduce 20 kinds of capacitor to you. I will illustrate them in three or four aspects: Structure, features, Usages, advantages and disadvantages.

Read More What is a Polypropylene Capacitor?UTMEL08 November 202120856

What is a Polypropylene Capacitor?UTMEL08 November 202120856A polypropylene capacitor is a kind of capacitor with a very stable electric capacity. It is often used in applications requiring very precise capacitance and can replace most polyphenylene or mica capacitors.

Read More What is the Difference between MOM, MIM and MOS Capacitors?UTMEL17 April 202567373

What is the Difference between MOM, MIM and MOS Capacitors?UTMEL17 April 202567373This article mainly introduces the structure, principle, advantages and disadvantages of MOM, MIM and MOS capacitors and the difference between them.

Read More What is a Power Capacitor?UTMEL20 November 20216229

What is a Power Capacitor?UTMEL20 November 20216229Power capacitors are capacitors used in power systems and electrical equipment. Any two pieces of metal conductors are separated by an insulating medium to form a capacitor. The size of the capacitor is determined by its size and the characteristics of the insulating medium between the two plates.

Read More

Subscribe to Utmel !

![MAX77840EVKIT#]() MAX77840EVKIT#

MAX77840EVKIT#Analog Devices

![MAXREFDES161#]() MAXREFDES161#

MAXREFDES161#Analog Devices

![MAX17576EVKITA#]() MAX17576EVKITA#

MAX17576EVKITA#Analog Devices

![MAX4060EVKIT]() MAX4060EVKIT

MAX4060EVKITAnalog Devices

![MAX774EVKIT-SO]() MAX774EVKIT-SO

MAX774EVKIT-SOAnalog Devices

![DS28E10EVKIT]() DS28E10EVKIT

DS28E10EVKITAnalog Devices

![MAX20444BEVKIT#]() MAX20444BEVKIT#

MAX20444BEVKIT#Analog Devices

![MAX9279COAXEVKIT#]() MAX9279COAXEVKIT#

MAX9279COAXEVKIT#Analog Devices

![MAX9293COAXEVKIT#]() MAX9293COAXEVKIT#

MAX9293COAXEVKIT#Analog Devices

![MAX5875EVKIT]() MAX5875EVKIT

MAX5875EVKITAnalog Devices

Product

Product Brand

Brand Articles

Articles Tools

Tools