Kintex-7 Series Technical Guide: Selection, Design, Alternatives

FPGAs

Deep dive into AMD (Xilinx) Kintex-7 FPGAs: key features, selection tips, design considerations, and alternatives. Includes XC7K420T specs, orderable MPNs, and official documentation pointers.

Product Introduction

Engineer’s Takeaway

Positioning: The Kintex-7 occupies the "mid-range" sweet spot in AMD’s 7 Series, sitting between the low-power Artix-7 and the high-performance Virtex-7. It is optimized for the best price-performance-per-watt.

Why it matters: It brings high-end transceiver capabilities (GTX up to 12.5 Gb/s) and massive DSP resources to applications that cannot justify the cost of a Virtex or Ultrascale device.

Market status: Active. Widely deployed in legacy and active LTE/5G wireless infrastructure, medical imaging, and avionics.

Lifecycle Check: This is a mature 28nm node product but remains a primary workhorse for designs requiring established toolchains (Vivado) and proven reliability.

The Kintex-7 family provides high-performance FPGA capabilities optimized for the best price-performance-per-watt, featuring high-speed serial transceivers and significant DSP resources for mid-range applications.

1. Technical Architecture and Core Advantages

The Kintex-7 architecture is built on a 28nm process (HKMG), designed to lower power consumption by up to 50% compared to previous generations (like Virtex-6) while offering similar raw performance. It integrates programmable logic with hard IP blocks for connectivity and processing.

1.1 How It Works (High-level)

At its core, the Kintex-7 fabric consists of Configurable Logic Blocks (CLBs) for parallel processing, coupled with dedicated block RAM (BRAM) for data buffering and DSP48E1 slices for arithmetic operations. The device communicates with the outside world via High-Range (HR) I/O banks (supporting 3.3V legacy standards) and High-Performance (HP) I/O banks (optimized for memory interfaces like DDR3).

1.2 Feature Matrix

| Feature | What it is | Why it matters (engineering value) |

|---|---|---|

| Logic Cells | Up to 416,960 (XC7K420T) | Provides massive parallel processing capability for complex state machines and IP cores. |

| DSP Slices | 1,440 DSP48E1 Slices | Critical for signal processing algorithms (FFT, FIR filters) in Radar and Ultrasound. |

| Transceivers | GTX (up to 12.5 Gb/s) | Enables high-speed protocols like 10GbE, PCIe Gen2, and CPRI without external PHYs. |

| Memory Interface | DDR3 Support (up to 1866 Mb/s) | High-bandwidth access to external DRAM, essential for video buffering and packet processing. |

| Block RAM | 28,620 Kb Total | Large on-chip cache reduces the need for frequent, power-hungry external memory access. |

Data source: XC7K420T Datasheet attributes

1.3 Deep Dive: Key Differentiators

Transceiver Dominance: The GTX transceivers in Kintex-7 are a defining feature. Capable of driving backplanes and optical modules directly, they support line rates up to 12.5 Gb/s. This allows a single mid-range chip to handle aggregation tasks that previously required multiple devices.

DSP Density: With 1,440 DSP slices, the XC7K420T specifically targets math-intensive workloads. Unlike standard logic, these hardened slices perform multiply-accumulate operations efficiently, critical for the digital front-end (DFE) of radio systems.

2. Naming / Variant Map and Selection Guide

2.1 Part Number Decoding

Understanding the suffix is vital for meeting environmental and timing constraints.

XC7K: Series Code (Kintex-7).

420T: Logic density indicator (~420k Logic Cells).

-1 / -2 / -3: Speed Grade. (-3 is the fastest, -1 is standard).

FFG: Package type (Flip-Chip BGA, Pb-free).

1156/901: Pin count.

I / E / C: Temperature Grade (I = Industrial, E = Extended/Commercial, C = Commercial).

2.2 Core Variant Comparison

| Variant | Key differences | Typical values | Best for |

|---|---|---|---|

| XC7K420T-1FFG1156I | Speed Grade -1, Industrial Temp (-40°C to 100°C) | Broadest temp range, standard timing | Industrial automation, outdoor comms infrastructure |

| XC7K420T-2FFG901I | Speed Grade -2, Industrial Temp, Reduced pin count (901) | Better timing margins than -1, smaller footprint | Space-constrained high-reliability systems |

| XC7K420T-3FFG1156E | Speed Grade -3, Commercial/Extended Temp (0°C to 100°C) | Maximum performance (fastest fabric/transceivers) | High-throughput networking inside data centers |

2.3 Quick Selection Checklist

Need max speed? Choose Speed Grade -3. Note that power consumption may be higher due to leakage at higher performance nodes.

Harsh environment? Ensure the suffix ends in I (Industrial) or Q (Automotive/Defense, if available in specific sub-lines).

I/O requirements? Check the package carefully. The FFG901 has fewer I/O pins than the FFG1156.

3. Key Specifications Explained

3.1 Power / Voltage / Operating Range

Core Voltage (Vccint): Typically 1.0V for 7-series devices [AI Added - Standard 7-Series Spec]. Precise tolerance depends on the speed grade (e.g., -2L or -1).

I/O Voltage: Two distinct banks:

HR Banks: Support up to 3.3V standards.

HP Banks: Designed for high-speed (standard 1.8V or lower, often used for DDR3).

Power Methodology: Power varies entirely based on resource utilization (logic toggle rate). Designers must use the Xilinx Power Estimator (XPE) or Vivado Report Power tool for accurate sizing.

3.2 Performance / Efficiency / Noise / Accuracy

Transceiver Speed: GTX transceivers are rated up to 12.5 Gb/s in this series. This enables direct support for PCIe Gen2 x8 and 10GBASE-R.

Memory Bandwidth: The hard memory controller supports DDR3 data rates up to 1866 Mb/s, providing substantial throughput for video buffering.

3.3 Thermal and Protection Behavior

Temperature Range:

Commercial (C): 0°C to 85°C (Junction)

Extended (E): 0°C to 100°C (Junction)

Industrial (I): -40°C to 100°C (Junction)

Thermal Management: High-utilization designs (especially those using many DSP slices and GTX lanes) will require significant heatsinking. Lidded flip-chip packages (FFG) help spread heat, but forced air is commonly required.

3.4 Fast Spec Table

| Parameter | Symbol | Min | Typ | Max | Unit | Notes |

|---|---|---|---|---|---|---|

| Logic Cells | - | - | 416,960 | - | Cells | XC7K420T Resource |

| DSP Slices | - | - | 1,440 | - | Slices | DSP48E1 |

| Block RAM | - | - | 28,620 | - | Kb | Total BRAM |

| GTX Rate | - | - | - | 12.5 | Gb/s | Max line rate |

| DDR3 Rate | - | - | - | 1866 | Mb/s | Max memory speed |

For full electrical characteristics, refer to the official datasheet ID XC7K420T.

4. Design Notes and Common Integration Issues

4.1 Reference Design Notes

PCB Stackup: Designs utilizing GTX transceivers (10G+) typically require low-loss dielectric materials (e.g., Megtron 6 or similar) and careful controlled impedance routing (100Ω differential).

Power Sequencing: FPGAs have strict power-up sequences (typically Vccint -> Vccbram -> Vccaux -> Vcco). Failing to sequence correctly can cause high inrush current or configuration failure.

Configuration: Supports JTAG, Serial Peripheral Interface (SPI) Flash (x1, x2, x4), and Byte Peripheral Interface (BPI). Quad SPI is the most common for boot loading in mid-range applications.

4.2 Layout / EMI / Thermal Checklist

Decoupling: Place low-ESR capacitors as close as possible to the BGA power balls. The 1156-pin package has a dense ball grid; via-in-pad or dog-bone fanout is often necessary.

Clocking: Route high-speed transceiver reference clocks (MGTREFCLK) differentially and shield them from noisy switching regulators.

Thermal Relief: Ensure the thermal interface material (TIM) covers the entire lid of the package.

4.3 Common Mistakes (Quick Debug)

| Context / Scenario | Symptom | Fix / Workaround |

|---|---|---|

| DDR3 Interface | Memory calibration failure or data corruption | Check HP Bank voltage (must be 1.5V for standard DDR3). Ensure termination resistors (ODT) are correctly configured in constraints. |

| Configuration | "Done" pin does not go high | Verify CFGBVS pin voltage setting matches the configuration bank voltage. Check SPI flash compatibility steps. |

| PCIe Link | Link training fails or falls back to Gen1 | Check transceiver reference clock jitter and ensure AC coupling capacitors are present on TX lanes. |

5. Typical Applications

5.1 Application 1: LTE/5G Base Station (Remote Radio Head)

Why Kintex-7?

Suitable due to the 1,440 DSP Slices which can efficiently handle Digital Down-Conversion (DDC) and Digital Up-Conversion (DUC) filters. The GTX Transceivers (up to 12.5 Gb/s) native support CPRI (Common Public Radio Interface) protocols essential for connecting the radio head to the baseband unit.

5.2 Application 2: Medical Ultrasound Imaging

Why Kintex-7?

Leverages the high I/O count (HP/HR banks) to interface with multi-channel ADC arrays (beamforming). The 28.6 Mb Block RAM acts as a crucial first-level buffer for high-bandwidth raw image data before processing and offloading via PCIe.

5.3 Application 3: High-End Wired Networking (Next-Gen Packet Processing)

Why Kintex-7?

The integrated PCI Express Gen2 hard block simplifies interfacing with host processors x86/ARM. The programmable logic allows for custom packet parsing and traffic management implementation at wire speed (10GbE+), bypassing software bottlenecks.

6. Competitors and Alternatives

6.1 Comparison Matrix

| Dimension | Kintex-7 (XC7K420T) | Intel Arria 10 (GX 480) | Microsemi PolarFire (MPF500T) |

|---|---|---|---|

| Architecture | 28nm TSMC [AI Added] | 20nm TSMC [AI Added] | 28nm SONOS (Non-volatile) [AI Added] |

| Target Market | Mid-Range Performance | Mid-to-High Range | Low Power / Security / Mid-Range |

| Transceivers | GTX (12.5 Gb/s) | GT (up to 17.4 Gb/s) [AI Added] | 12.7 Gb/s [AI Added] |

| Static Power | Moderate | Moderate/High | Lowest (Non-volatile fabric) [AI Added] |

| Ecosystem Tools | Vivado Design Suite | Quartus Prime | Libero SoC |

Note: Any non-official additions are labeled [AI Added]. The comparison highlights general market positioning. Arria 10 is technically a generation newer in process node (20nm vs 28nm), offering higher performance ceilings but typically at different price points.

6.2 Alternative Paths

✅ Pin-to-pin alternatives: Generally none across different vendors. Within the Xilinx ecosystem, migration between 7-series devices (e.g., Artix to Kintex) usually requires PCB re-spin due to different package footprints, though some footprint-compatible migration paths exist within the same package code (e.g., FFG901).

🟡 Functional alternatives:

Intel Arria 10: If higher transceiver speeds (>12.5 Gb/s) are needed.

Microsemi PolarFire: If low static power or "instant-on" capability is critical (due to flash-based architecture).

🔴 Not recommended:

Spartan-7 / Artix-7: If your design relies heavily on 10Gbps+ transceivers or massive DSP counts, these lower-tier families will not meet the spec.

7. FAQ

Q1: What software is required to design for Kintex-7?

A: Kintex-7 is fully supported by the AMD (Xilinx) Vivado Design Suite. It is not supported by the legacy ISE Design Suite (which stopped at Virtex-6/Spartan-6). You can use the free Vivado ML Standard Edition (formerly WebPACK) for smaller devices, but the larger XC7K420T typically requires a paid Enterprise license or a specific device license.

Q2: Can Kintex-7 support PCIe Gen3?

A: The Kintex-7 integrated block for PCI Express technically supports widely deployed Gen2 x8. While the GTX transceivers (12.5 Gb/s) are physically capable of Gen3 speeds (8.0 GT/s), the hard IP block in standard Kintex-7 is Gen2. Achieving Gen3 usually requires soft-core IP implementation or moving to Kintex UltraScale devices.

Q3: What is the difference between HP and HR I/O banks?

A: HP (High-Performance) banks are optimized for high-speed memory interfaces and LVDS, supporting voltages up to 1.8V. HR (High-Range) banks are designed to support wider voltage standards, including legacy 3.3V and 2.5V I/O, making them suitable for control signals and interfacing with older peripherals.

8. Orderable MPN List

Prices and real-time inventory change frequently. Do not fabricate.

| MPN | Description | Status |

|---|---|---|

| XC7K420T-1FFG1156I | Kintex-7, 420k Logic Cells, Speed -1, Ind Temp, 1156-pin | 🟢 In Stock (Typical) |

| XC7K420T-2FFG901I | Kintex-7, 420k Logic Cells, Speed -2, Ind Temp, 901-pin | 🟢 In Stock (Typical) |

| XC7K420T-3FFG1156E | Kintex-7, 420k Logic Cells, Speed -3, Com Temp, 1156-pin | 🟡 Check Availability |

Legend:

🟢 In Stock

🟡 Limited

🔴 Obsolete

9. Resources and Downloads

9.1 Official Documents

| Document | ID / Name | Notes |

|---|---|---|

| Datasheet | DS180 / DS182 (Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics) | Essential for timing and power specs. |

| Selection Guide | 7 Series FPGAs Overview (DS180) | High-level feature comparison. |

| User Guide | UG476 (7 Series FPGAs GTX/GTH Transceivers User Guide) | Critical for designing high-speed links. |

| User Guide | UG474 (7 Series FPGAs Configurable Logic Block User Guide) | Deep dive into CLB architecture. |

9.2 Tools / Software

Vivado Design Suite: The primary IDE for synthesis, implementation, and bitstream generation.

Xilinx Power Estimator (XPE): Spreadsheet-based tool for estimating power budget before board design.

9.3 Support

AMD Xilinx Support Forums: Community support for debug and design questions.

Reference Designs: Check official application notes for PCIe and DDR3 reference layouts.

Disclaimer

This article is for selection and design reference only. Always verify final specifications and electrical limits against the latest official AMD (Xilinx) documentation.

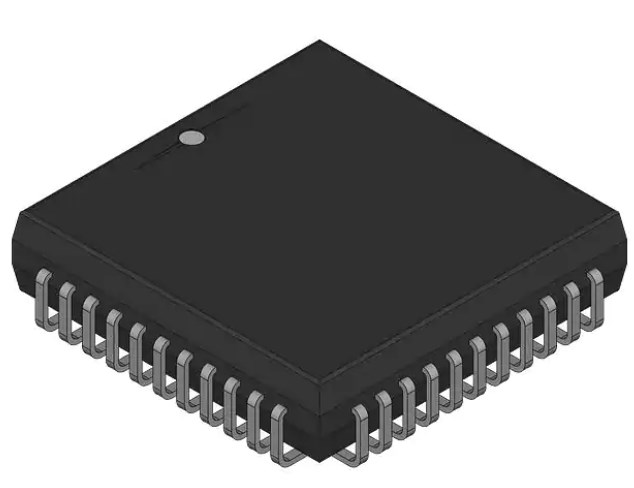

Specifications

- TypeParameter

- Surface Mount

having leads that are designed to be soldered on the side of a circuit board that the body of the component is mounted on.

YES - Number of Terminals1156

- Rohs CodeYes

- Part Life Cycle CodeTransferred

- Ihs ManufacturerXILINX INC

- Part Package CodeBGA

- Package DescriptionLEAD FREE, FBGA-1156

- Moisture Sensitivity Levels4

- Package Body MaterialPLASTIC/EPOXY

- Package StyleGRID ARRAY

- JESD-609 Code

The "JESD-609 Code" in electronic components refers to a standardized marking code that indicates the lead-free solder composition and finish of electronic components for compliance with environmental regulations.

e1 - Terminal Finish

Terminal Finish refers to the surface treatment applied to the terminals or leads of electronic components to enhance their performance and longevity. It can improve solderability, corrosion resistance, and overall reliability of the connection in electronic assemblies. Common finishes include nickel, gold, and tin, each possessing distinct properties suitable for various applications. The choice of terminal finish can significantly impact the durability and effectiveness of electronic devices.

TIN SILVER COPPER - HTS Code

HTS (Harmonized Tariff Schedule) codes are product classification codes between 8-1 digits. The first six digits are an HS code, and the countries of import assign the subsequent digits to provide additional classification. U.S. HTS codes are 1 digits and are administered by the U.S. International Trade Commission.

8542.39.00.01 - Terminal Position

In electronic components, the term "Terminal Position" refers to the physical location of the connection points on the component where external electrical connections can be made. These connection points, known as terminals, are typically used to attach wires, leads, or other components to the main body of the electronic component. The terminal position is important for ensuring proper connectivity and functionality of the component within a circuit. It is often specified in technical datasheets or component specifications to help designers and engineers understand how to properly integrate the component into their circuit designs.

BOTTOM - Terminal Form

Occurring at or forming the end of a series, succession, or the like; closing; concluding.

BALL - Peak Reflow Temperature (Cel)

Peak Reflow Temperature (Cel) is a parameter that specifies the maximum temperature at which an electronic component can be exposed during the reflow soldering process. Reflow soldering is a common method used to attach electronic components to a circuit board. The Peak Reflow Temperature is crucial because it ensures that the component is not damaged or degraded during the soldering process. Exceeding the specified Peak Reflow Temperature can lead to issues such as component failure, reduced performance, or even permanent damage to the component. It is important for manufacturers and assemblers to adhere to the recommended Peak Reflow Temperature to ensure the reliability and functionality of the electronic components.

250 - Reach Compliance Code

Reach Compliance Code refers to a designation indicating that electronic components meet the requirements set by the Registration, Evaluation, Authorization, and Restriction of Chemicals (REACH) regulation in the European Union. It signifies that the manufacturer has assessed and managed the chemical substances within the components to ensure safety and environmental protection. This code is vital for compliance with regulations aimed at minimizing risks associated with hazardous substances in electronic products.

compliant - Time@Peak Reflow Temperature-Max (s)

Time@Peak Reflow Temperature-Max (s) refers to the maximum duration that an electronic component can be exposed to the peak reflow temperature during the soldering process, which is crucial for ensuring reliable solder joint formation without damaging the component.

30 - Pin Count

a count of all of the component leads (or pins)

1156 - Qualification Status

An indicator of formal certification of qualifications.

Not Qualified - Programmable Logic Type

Generally, programmable logic devices can be described as being one of three different types: Simple programmable logic devices (SPLD) Complex programmable logic devices (CPLD) Field programmable logic devices (FPGA).

FIELD PROGRAMMABLE GATE ARRAY

Parts with Similar Specs

Datasheet PDF

- Datasheets :

AD9833 Digitally Programming Waveform Generator:Pinout,Datasheet,Description

AD9833 Digitally Programming Waveform Generator:Pinout,Datasheet,Description18 September 20215674

![TL431ACLP Shunt Voltage Reference IC Adjustable 2.495V 100mA[FAQ]: Datasheet, Features, and Pinout](https://res.utmel.com/Images/Article/4ac425df-f9a3-4fa9-84f6-68008d9b38f1.jpg) TL431ACLP Shunt Voltage Reference IC Adjustable 2.495V 100mA[FAQ]: Datasheet, Features, and Pinout

TL431ACLP Shunt Voltage Reference IC Adjustable 2.495V 100mA[FAQ]: Datasheet, Features, and Pinout16 March 2022739

PIC16LF1824TIST Microcontroller Datasheet Overview

PIC16LF1824TIST Microcontroller Datasheet Overview29 February 2024123

![How to Run IRFP250 Transistor Safely? [FAQ& Video]](https://res.utmel.com/Images/Article/baa907de-272a-42c4-8930-aa53614d9c2d.jpg) How to Run IRFP250 Transistor Safely? [FAQ& Video]

How to Run IRFP250 Transistor Safely? [FAQ& Video]25 April 20225008

AD7891AP-1REEL IC DAS: Feature, Circuit,Specification

AD7891AP-1REEL IC DAS: Feature, Circuit,Specification14 August 2024664

2N4401 NPN Transistor: Datasheet, Pinout, and Equivalent

2N4401 NPN Transistor: Datasheet, Pinout, and Equivalent25 August 202116406

CN3065 Mini Solar Charger Module: How to use the CN3065?

CN3065 Mini Solar Charger Module: How to use the CN3065?16 May 20255794

PC123 Photocoupler: PC123 vs.PC817, Equivalents, Datasheet

PC123 Photocoupler: PC123 vs.PC817, Equivalents, Datasheet08 October 202118186

An Overview of Crystal Oscillator

An Overview of Crystal Oscillator21 September 202013316

The Different Types of Circuit Breakers and Their Applications

The Different Types of Circuit Breakers and Their Applications11 April 20236281

8051 Microcontroller: History, Architecture, Applications, and Features

8051 Microcontroller: History, Architecture, Applications, and Features20 February 202120250

What is Graphics Processing Unit (GPU)?

What is Graphics Processing Unit (GPU)?18 October 20217355

What is a Ceramic Filter?

What is a Ceramic Filter?10 April 20214256

Introduction to 6 Common Power Supply Design Circuits

Introduction to 6 Common Power Supply Design Circuits09 April 20225832

DoD Allocates $238 Million for Semiconductor Centers under CHIPS and Science Act

DoD Allocates $238 Million for Semiconductor Centers under CHIPS and Science Act23 September 20232742

Designing Application-Specific Integrated Circuits

Designing Application-Specific Integrated Circuits07 March 20251920

AMD Xilinx

In Stock: 442

United States

China

Canada

Japan

Russia

Germany

United Kingdom

Singapore

Italy

Hong Kong(China)

Taiwan(China)

France

Korea

Mexico

Netherlands

Malaysia

Austria

Spain

Switzerland

Poland

Thailand

Vietnam

India

United Arab Emirates

Afghanistan

Åland Islands

Albania

Algeria

American Samoa

Andorra

Angola

Anguilla

Antigua & Barbuda

Argentina

Armenia

Aruba

Australia

Azerbaijan

Bahamas

Bahrain

Bangladesh

Barbados

Belarus

Belgium

Belize

Benin

Bermuda

Bhutan

Bolivia

Bonaire, Sint Eustatius and Saba

Bosnia & Herzegovina

Botswana

Brazil

British Indian Ocean Territory

British Virgin Islands

Brunei

Bulgaria

Burkina Faso

Burundi

Cabo Verde

Cambodia

Cameroon

Cayman Islands

Central African Republic

Chad

Chile

Christmas Island

Cocos (Keeling) Islands

Colombia

Comoros

Congo

Congo (DRC)

Cook Islands

Costa Rica

Côte d’Ivoire

Croatia

Cuba

Curaçao

Cyprus

Czechia

Denmark

Djibouti

Dominica

Dominican Republic

Ecuador

Egypt

El Salvador

Equatorial Guinea

Eritrea

Estonia

Eswatini

Ethiopia

Falkland Islands

Faroe Islands

Fiji

Finland

French Guiana

French Polynesia

Gabon

Gambia

Georgia

Ghana

Gibraltar

Greece

Greenland

Grenada

Guadeloupe

Guam

Guatemala

Guernsey

Guinea

Guinea-Bissau

Guyana

Haiti

Honduras

Hungary

Iceland

Indonesia

Iran

Iraq

Ireland

Isle of Man

Israel

Jamaica

Jersey

Jordan

Kazakhstan

Kenya

Kiribati

Kosovo

Kuwait

Kyrgyzstan

Laos

Latvia

Lebanon

Lesotho

Liberia

Libya

Liechtenstein

Lithuania

Luxembourg

Macao(China)

Madagascar

Malawi

Maldives

Mali

Malta

Marshall Islands

Martinique

Mauritania

Mauritius

Mayotte

Micronesia

Moldova

Monaco

Mongolia

Montenegro

Montserrat

Morocco

Mozambique

Myanmar

Namibia

Nauru

Nepal

New Caledonia

New Zealand

Nicaragua

Niger

Nigeria

Niue

Norfolk Island

North Korea

North Macedonia

Northern Mariana Islands

Norway

Oman

Pakistan

Palau

Palestinian Authority

Panama

Papua New Guinea

Paraguay

Peru

Philippines

Pitcairn Islands

Portugal

Puerto Rico

Qatar

Réunion

Romania

Rwanda

Samoa

San Marino

São Tomé & Príncipe

Saudi Arabia

Senegal

Serbia

Seychelles

Sierra Leone

Sint Maarten

Slovakia

Slovenia

Solomon Islands

Somalia

South Africa

South Sudan

Sri Lanka

St Helena, Ascension, Tristan da Cunha

St. Barthélemy

St. Kitts & Nevis

St. Lucia

St. Martin

St. Pierre & Miquelon

St. Vincent & Grenadines

Sudan

Suriname

Svalbard & Jan Mayen

Sweden

Syria

Tajikistan

Tanzania

Timor-Leste

Togo

Tokelau

Tonga

Trinidad & Tobago

Tunisia

Turkey

Turkmenistan

Turks & Caicos Islands

Tuvalu

U.S. Outlying Islands

U.S. Virgin Islands

Uganda

Ukraine

Uruguay

Uzbekistan

Vanuatu

Vatican City

Venezuela

Wallis & Futuna

Yemen

Zambia

Zimbabwe

Product

Product Brand

Brand Articles

Articles Tools

Tools